Advanced Power Amplifier Architectures to Support 5G+ Cellular Infrastructure

by

Maruf Ahmed

## A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved July 2022 by the Graduate Supervisory Committee:

Jennifer Kitchen, Chair James Aberle Bertan Bakkaloglu Sule Ozev

ARIZONA STATE UNIVERSITY

August 2022

#### ABSTRACT

The world has seen a revolution in cellular communication with the advent of 5G, which enables gigabits per second data speed with low latency, massive capacity, and increased availability. Complex modulated signals are used in these modern communication systems to achieve high spectral efficiency, and these signals exhibit high peak to average power ratios (PAPR). Design of cellular infrastructure hardware to support these complex signals therefore becomes challenging, as the transmitter's radio frequency power amplifier (RF PA) needs to remain highly efficient at both peak and backed off power conditions. Additionally, these PAs should exhibit high linearity and support continually increasing bandwidths. Many advanced PA configurations exhibit high efficiency for processing legacy communications signals. Some of the most popular architectures are Envelope Elimination and Restoration (EER), Envelope Tracking (ET), Linear Amplification using Non-linear Component (LINC), Doherty Power Amplifiers (DPA), and Polar Transmitters. Among these techniques, the DPA is the most widely used architecture for base-station applications because of its simple configuration and ability to be linearized using simple digital pre-distortion (DPD) algorithms. To support the cellular infrastructure needs of 5G and beyond, RF PAs, specifically DPA architectures, must be further enhanced to support broader bandwidths as well as smaller form-factors with higher levels of integration. The following four novel works are presented in this dissertation to support RF PA requirements for future cellular infrastructure:

- 1. A mathematical analysis to analyze the effects of non-linear parasitic capacitance  $(C_{ds})$  on the operation of continuous class-F (CCF) mode power amplifiers and identify their optimum operating range for high power and efficiency.

- 2. A methodology to incorporate a class-J harmonic trapping network inside the

PA package by considering the effect of non-linear  $C_{ds}$ , thus reducing the DPA footprint while achieving high RF performance.

- 3. A novel method of synthesizing the DPA's output combining network (OCN) to realize an integrated two-stage integrated LDMOS asymmetric DPA.

- 4. A novel extended back-off efficiency range DPA architecture that engineers the mutual interaction between combining load and peaking off-state impedance. The theory and architecture are verified through a GaN-based DPA design.

## DEDICATION

To my wife, Sadiya

#### ACKNOWLEDGMENTS

First and foremost, I would like to convey my profound gratitude and sincere thanks to my PhD supervisor, Dr. Jennifer Kitchen for her invaluable guidance. Her unfailing patience, erudite advice and constant encouragement helped me to a great extent in accomplishing my work. I want to also thank Dr. Bertan Bakkaloglu, Dr. James Aberle and Dr. Sule Ozev for being part of my PhD committee and providing their invaluable comments and feedbacks whenever necessary.

My solemn gratitude to Joseph Staudinger for his insightful guidance and in-depth technical knowledge that he shared with me over the years. I want to thank my coworkers from NXP and fellow researchers from ASU- Karen Jacobs, Margaret Szymanowsky, Roy Mclaren, Mir Masood, Tai Nguy, Debatrayee Roychowdhury, Pierre Almairac and Xavier Hue, for their contribution to this work in many different ways.

I am especially thankful to my wife Sadiya Jahan. It would have been simply impossible to complete my PhD without her tremendous sacrifice and constant support with maintaining our family. Whenever I was at the brink of giving up, her love and encouragement put me back on track. I am absolutely blessed to have my two kids- Nawaf and Maheera who have always been beaming sources of inspiration to my work. My sincere respect and gratefulness towards my parent-in-laws who stayed with us in times of need and offered their generous help and support to carry out my work.

Finally, I am enormously grateful to my parents, brother and sister for their unconditional support, love and trust that worked as driving force to continue my work and bring it to completion.

| TABLE OF | CONTENTS |

|----------|----------|

|----------|----------|

|      |       | Pa                                                         | age  |

|------|-------|------------------------------------------------------------|------|

| LIST | ОFЛ   | TABLES                                                     | vii  |

| LIST | OF F  | FIGURES                                                    | viii |

| CHA  | PTER  | R                                                          |      |

| 1    | INT   | RODUCTION                                                  | 1    |

|      |       | 1.0.1 Harmonic Tuned and Continuous-mode PA Operation      | 5    |

|      |       | 1.0.2 Fundamental Operation of the Doherty Power Amplifier | 12   |

|      | 1.1   | Organization of the Work                                   | 15   |

| 2    | NOI   | N-LINEAR $C_{DS}$ EFFECT ON CONTINUOUS CLASS-F MODE        |      |

|      | POV   | WER AMPLIFIERS                                             | 17   |

|      | 2.1   | Introduction                                               | 17   |

|      | 2.2   | Theory of CCF PAs                                          | 19   |

|      | 2.3   | Effect of Non-linear $C_{ds}$ on CCF Mode PAs              | 20   |

|      | 2.4   | Summary                                                    | 27   |

| 3    | АН    | IGH PERFORMANCE CLASS-J DOHERTY POWER AMPLIFIER            | 28   |

|      | 3.1   | Introduction                                               | 28   |

|      | 3.2   | Class-BJ/ Continuous Class-J Amplification                 | 29   |

|      | 3.3   | Doherty Amplifier Design                                   | 30   |

|      | 3.4   | Measured DPA Performance                                   | 34   |

|      | 3.5   | Summary                                                    | 36   |

| 4    | 2.6-0 | GHZ INTEGRATED LDMOS DOHERTY POWER AMPLIFIER               |      |

|      | FOF   | R 5G BASESTATION APPLICATIONS                              | 37   |

|      | 4.1   | Introduction                                               | 37   |

|      | 4.2   | Theory of Operation                                        | 38   |

|      | 4.3   | DPA Design and Measurement Results                         | 42   |

| CHAI | PTEF | ł      |                                                   | Page |

|------|------|--------|---------------------------------------------------|------|

|      | 4.4  | Summ   | ary                                               | 46   |

| 5    | ΑN   | OVEL I | EXTENDED BACK-OFF EFFICIENCY RANGE DOHERTY        | Y    |

|      | POV  | VER A  | MPLIFIER                                          | 47   |

|      | 5.1  | Introd | uction                                            | 47   |

|      | 5.2  | Theor  | y                                                 | 51   |

|      |      | 5.2.1  | Conventional Doherty Combiner and Its Limitations | 51   |

|      |      | 5.2.2  | Proposed COCL Doherty Operating Principle         | 56   |

|      |      | 5.2.3  | Derivation of the ABCD Parameters                 | 66   |

|      | 5.3  | Design | and Simulation Results                            | 73   |

|      | 5.4  | Measu  | rement Results                                    | 83   |

|      | 5.5  | Summ   | ary                                               | 88   |

| 6    | COI  | NCLUS  | ION                                               | 89   |

| REFF | EREN | CES    |                                                   | 91   |

## LIST OF TABLES

| Table | F                                                                                            | Page |

|-------|----------------------------------------------------------------------------------------------|------|

| 1.1   | Basic PA Classes                                                                             | 2    |

| 3.1   | DPA Performance Under Multi-Carrier LTE Stimulus                                             | 34   |

| 3.2   | Comparison with Other 3.5 GHz DPAs                                                           | 36   |

| 4.1   | ABCD Parameters for Figure 4.2(b)                                                            | 41   |

| 4.2   | DPA Performance Summary and Comparison with State-of-the-Art                                 | 45   |

| 5.1   | Comparison Among Different Doherty Configurations                                            | 49   |

| 5.2   | $x_c$ for Different Values of $x_o$ and $\alpha$ When, $OBO_{ex} = 8.5$ and $9.5 \ dB \dots$ | 62   |

| 5.3   | Types of OMN Combination and Required Adjustment of Phase from                               |      |

|       | the Input                                                                                    | 70   |

| 5.4   | Calculated ABCD Parameters for Ideal COCL DPA Combiner                                       | 75   |

| 5.5   | Modified ABCD Parameters after Incorporating Carrier and Peaking                             |      |

|       | Parasitic Networks                                                                           | 77   |

| 5.6   | Performance Comparison with State-of-the-Art Extended Back-off Range                         |      |

|       | DPAs                                                                                         | 87   |

## LIST OF FIGURES

| Figure | Pa                                                                           | age |

|--------|------------------------------------------------------------------------------|-----|

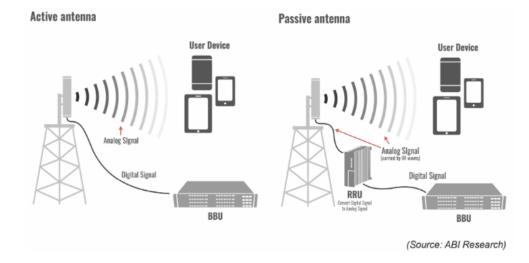

| 1.1    | Active vs Passive Antenna                                                    | 1   |

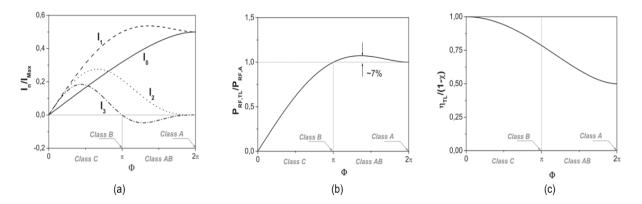

| 1.2    | (a) Normalized fourier current components, (b) normalized power with         |     |

|        | respect to class-A, and (c) Efficiency for different classes of operation    | 2   |

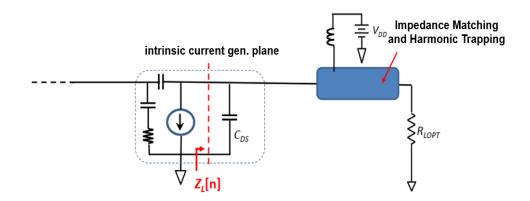

| 1.3    | Simple PA output model                                                       | 4   |

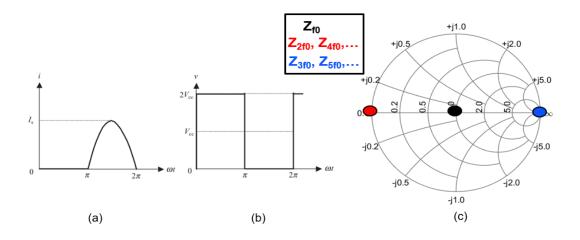

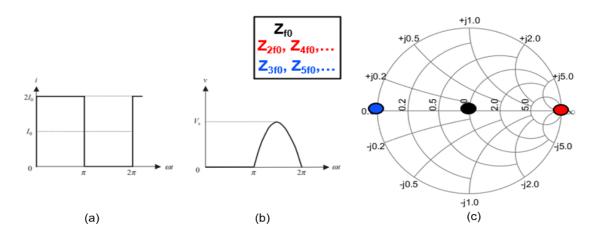

| 1.4    | Ideal class-F (a) voltage, (b) current, and (c) impedance locations on       |     |

|        | smith chart                                                                  | 5   |

| 1.5    | Ideal class- $F^{-1}$ (a) current, (b) voltage, and (c) impedance locations  |     |

|        | on smith chart                                                               | 6   |

| 1.6    | $f_0$ (black) and $2f_0$ (red) impedance locations on smith chart for (a)    |     |

|        | class-B, (b) class-J, and (c) voltage and current waveforms for class-J      | 7   |

| 1.7    | Class-BJ (a) voltage and current waveforms, (b) impedance locations          |     |

|        | on smith chart                                                               | 9   |

| 1.8    | CCF (a) voltage and current waveforms, (b) impedance locations on            |     |

|        | smith chart                                                                  | 10  |

| 1.9    | $\rm CCF^{-1}$ (a) voltage and current waveforms, (b) impedance locations on |     |

|        | smith chart                                                                  | 11  |

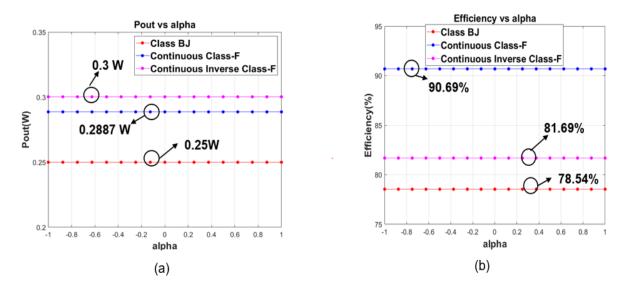

| 1.10   | (a) Normalized output power, and (b) efficiency for all continuous mode      |     |

|        | PAs                                                                          | 11  |

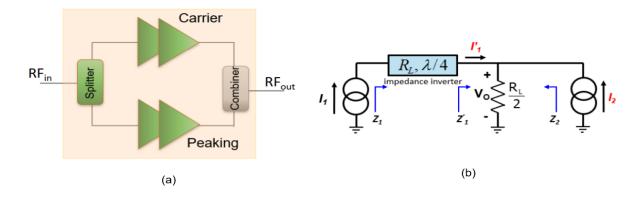

| 1.11   | (a) A DPA block diagram, and (b) a simplified current source model           |     |

|        | of a DPA                                                                     | 12  |

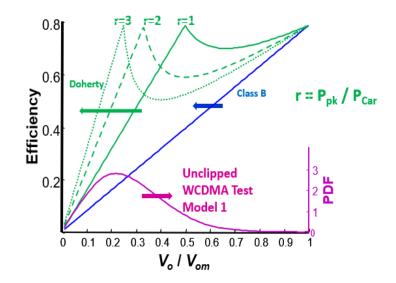

| 1.12   | DPA efficiency with respect to normalized output voltage for different       |     |

|        | power ratio                                                                  | 13  |

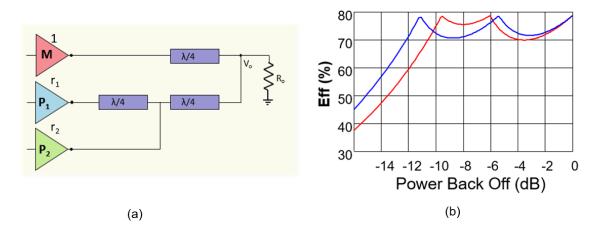

| 1.13   | 3-way DPA, (a)block diagram, and (b) efficiency for different power ratio    | 14  |

| 2.1 | Fundamental and harmonic locations for (a) class-B PA, and (b) class-               |    |

|-----|-------------------------------------------------------------------------------------|----|

|     | BJ PA                                                                               | 17 |

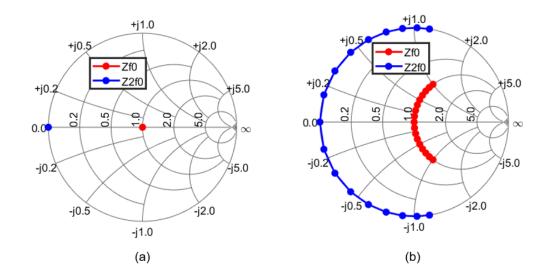

| 2.2 | (a) Impedance locations for ideal CCF mode, and (b) CCF voltage and                 |    |

|     | current waveforms                                                                   | 19 |

| 2.3 | (a) Capacitance versus drain voltage for non-linear $C_{ds}$ with various           |    |

|     | fitting parameters, (b) simplified equivalent circuit model of the PA               |    |

|     | device under operation, (c) calculated time domain voltage and current              |    |

|     | waveforms for $-1 \le \alpha \le 1$ at the LDP for CCF mode                         | 21 |

| 2.4 | $f_0, 2f_0, and 3f_0$ impedance trajectories at the LDP                             | 22 |

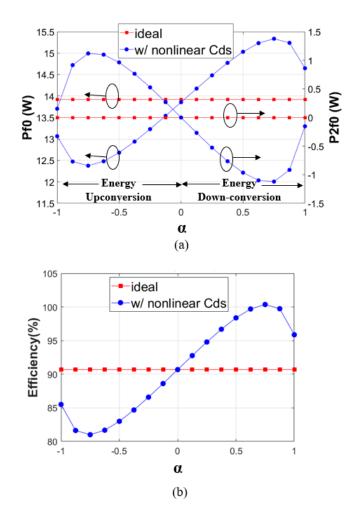

| 2.5 | (a) Calculated $f_0$ and $2f_0$ power, (b) calculated efficiency                    | 24 |

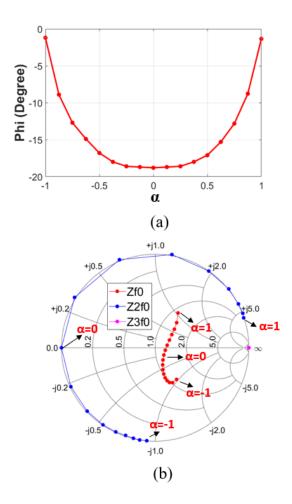

| 2.6 | (a) Phase shift $\phi$ vs alpha, (b) Impedance trajectories after $\phi$ is applied | 25 |

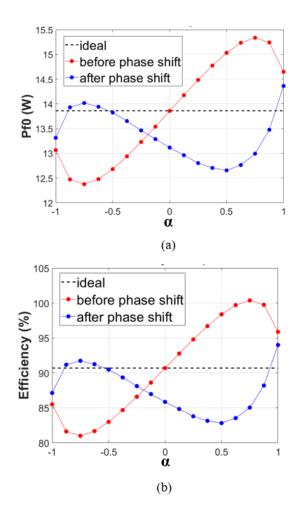

| 2.7 | (a) Power before and after phase shift, and (b) efficiency before and               |    |

|     | after phase shift                                                                   | 26 |

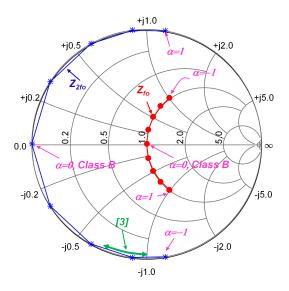

| 3.1 | Class-B/J fundamental (red) and second harmonic (blue) load impedance               |    |

|     | at intrinsic device plane (linear $C_{ds}$ ), and (green) enhanced efficiency       |    |

|     | region of $\alpha$ reported in [4] for non-linear $C_{ds}$                          | 29 |

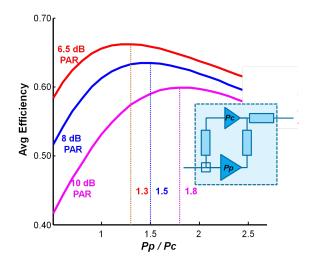

| 3.2 | Average 2-way Doherty efficiency for $6.5$ , $8$ , and $10 \text{ dB PAPR signals}$ |    |

|     | as a function of peaking to carrier power (ideal Doherty operation) $\ldots$        | 30 |

| 3.3 | Simplified schematic of output matching circuit for Carrier sub-amplifier)          | 31 |

| 3.4 | Illustration of DPA elements in a QFN package                                       | 32 |

| 3.5 | Full Doherty amplifier including QFN package, and external input cou-               |    |

|     | pler and output combiner                                                            | 33 |

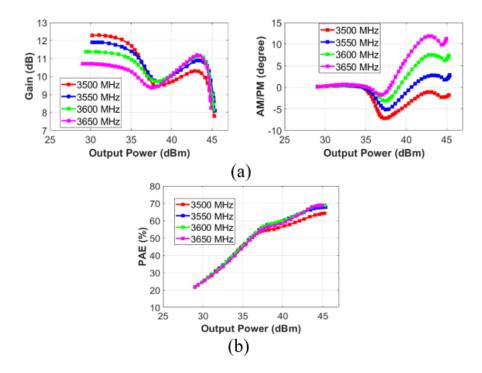

| 3.6 | Measured DPA performance under CW drive-up stimulus, (a) gain and                                         |    |

|-----|-----------------------------------------------------------------------------------------------------------|----|

|     | am/pm response, and (b) PAE                                                                               | 33 |

| 3.7 | Doherty output spectral response under a 5 carrier LTE signal at $20$                                     |    |

|     | MHz / carrier, after DPD correction                                                                       | 35 |

| 4.1 | Proposed integrated Doherty output combining network (OCN)                                                | 38 |

| 4.2 | (a) Quasi impedance inverter, and (b) Parasitic components of the                                         |    |

|     | quasi impedance transformer replaced by ABCD network                                                      | 39 |

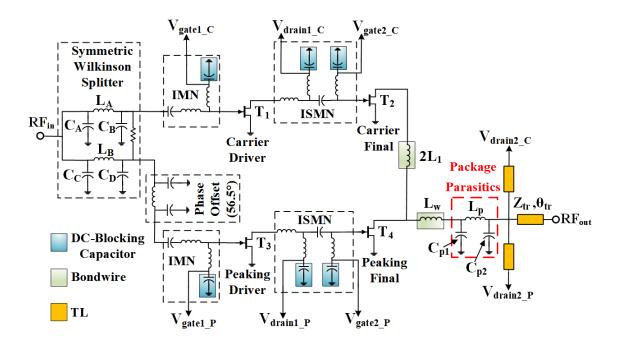

| 4.3 | Schematic of proposed two-stage integrated Doherty                                                        | 40 |

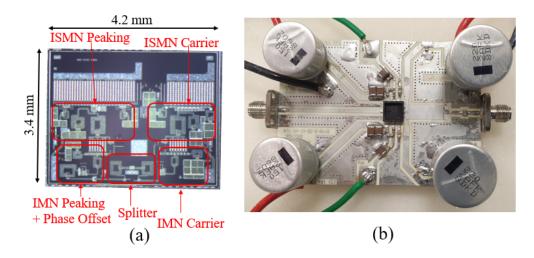

| 4.4 | (a) Chip micrograph of the Doherty RFIC, and (b) Evaluation board                                         | 42 |

| 4.5 | (a) Measured Gain, PAE, and AM/PM performance of the DPA under                                            |    |

|     | CW signal, and (b) DPD performance with two-carrier 160 MHz LTE $$ .                                      | 45 |

| 5.1 | Generalized combiner network for conventional Doherty                                                     | 47 |

| 5.2 | Generalized combiner network for the proposed COCL Doherty                                                | 54 |

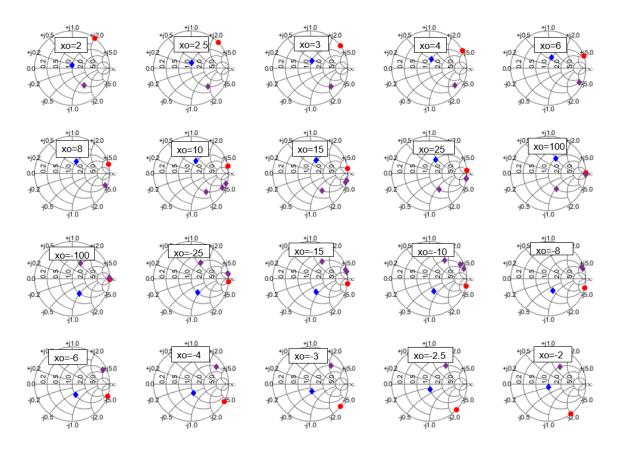

| 5.3 | Location of $Z_c = R_c(1 + jx_c)$ (blue and purple) for different values                                  |    |

|     | $Z_{off} = jR_c x_o \text{ (red)}$ when $\alpha = 1.5, OBO_{ex} = 9.5 \text{ dB}$ and $R_c = 15\Omega$ on |    |

|     | smith charts. Charts are normalized to $R_c$ .                                                            | 58 |

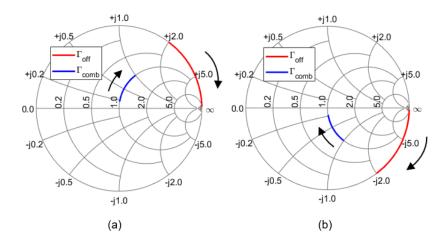

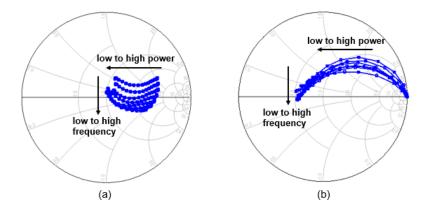

| 5.4 | Locus of $\Gamma_{off}$ and $\Gamma_{comb}$ in the (a) inductive design space and (b)                     |    |

|     | capacitive design space                                                                                   | 61 |

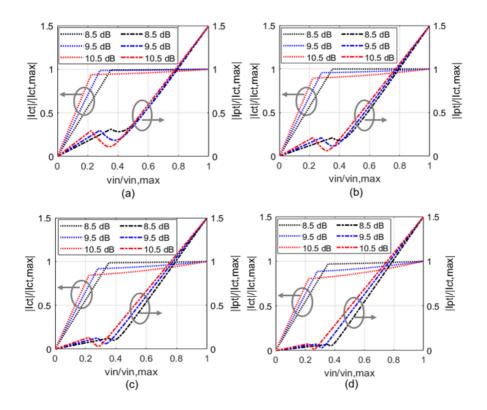

| 5.5 | Combining currents $(I_{ct} \text{ and } I_{pt})$ plots obtained from analysis for (a)                    |    |

|     | $ x_o  = 3$ , (b) $ x_o  = 4.5$ , (c) $ x_o  = 8$ , and (d) $ x_o  = 15$ when, for each                   |    |

|     | cases $OBO_{ex} = 8.5, 9.5$ and $10.5 \ dB$                                                               | 71 |

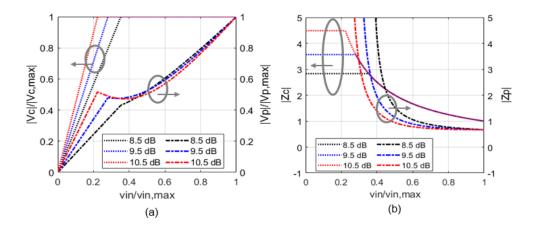

| 5.6 | (a) Intrinsic voltage ( $V_c$ and $V_p$ ) and (b) load impedances ( $Z_c$ and $Z_p$                       |    |

|     | ) plots obtained from analysis when $OBO_{ex} = 8.5, 9.5$ and $10.5 \ dB$                                 | 72 |

| Page |

|------|

|------|

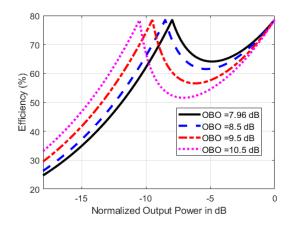

| 5.7  | Calculated efficiency plot for proposed COCL DPA when $\alpha = 1.5$          | 73 |

|------|-------------------------------------------------------------------------------|----|

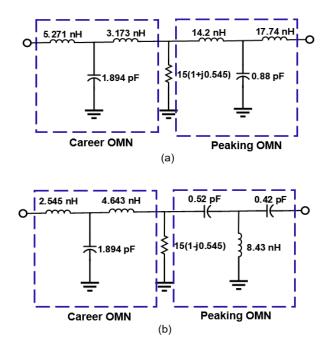

| 5.8  | Example lumped component based ideal COCL Doherty combiner,                   |    |

|      | when (a) $x_o = 4.5$ , and (b) $x_o = -4.5$                                   | 74 |

| 5.9  | Simulation results of ideal COCL combiners of Figure 5.8. Simulated           |    |

|      | (a) impedance trajectories, and (b) efficiency                                | 75 |

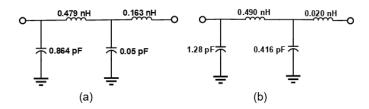

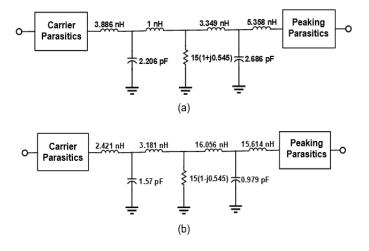

| 5.10 | (a) Carrier (CGH40006S) parasitic network (b) Peaking (CGH40010F)             |    |

|      | parasitic network                                                             | 78 |

| 5.11 | Modified combiner of (a) Figure 5.8 (a), and (b) Figure 5.8(b) after          |    |

|      | incorporating the parasitic networks from Figure 5.10                         | 78 |

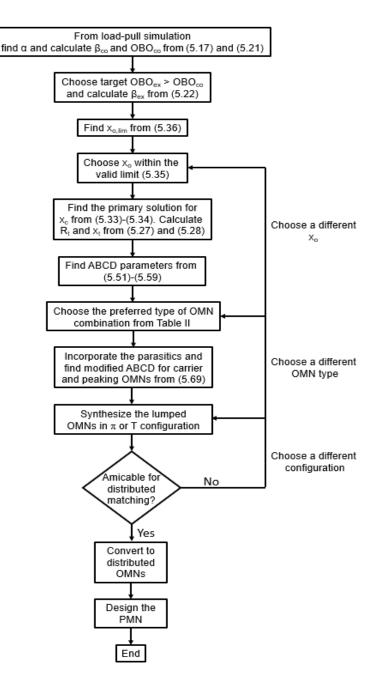

| 5.12 | Design flow chart                                                             | 79 |

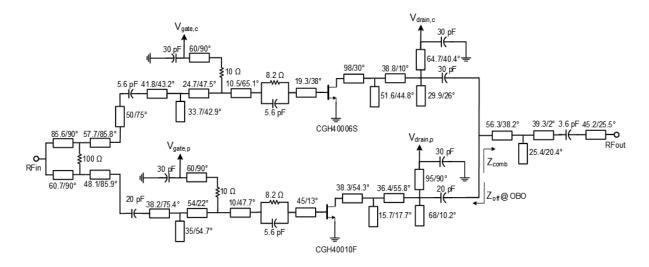

| 5.13 | Full schematic of the prototype COCL Doherty                                  | 80 |

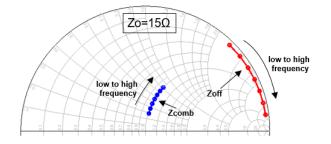

| 5.14 | Simulated $Z_{off}$ and $Z_{comb}$ trajectories on smith chart for 1.7-2 GHz  | 80 |

| 5.15 | Simulated (a) $Z_c$ and (b) $Z_p$ trajectories on prototype Doherty for 1.7-2 |    |

|      | GHz                                                                           | 82 |

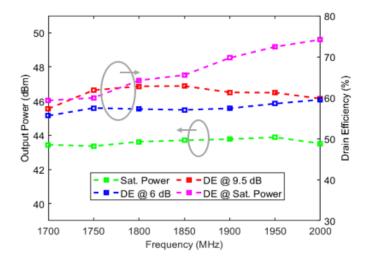

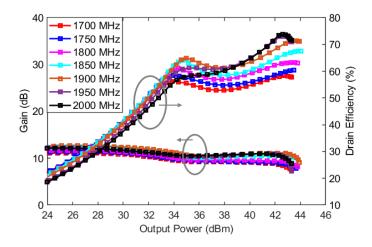

| 5.16 | Simulated saturated power and efficiency at different power levels ver-       |    |

|      | sus frequency for the prototype Doherty                                       | 82 |

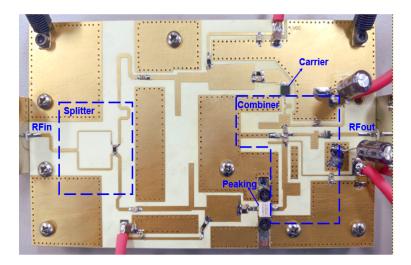

| 5.17 | Snapshot of fabricated Doherty PCB                                            | 83 |

| 5.18 | Measured efficiency and gain versus output power for CW signal                | 84 |

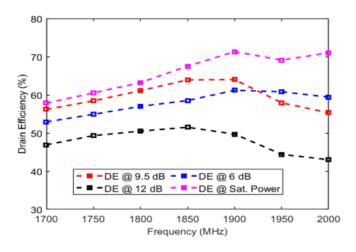

| 5.19 | Measured drain efficiency for different power levels versus frequency         |    |

|      | for CW signal                                                                 | 84 |

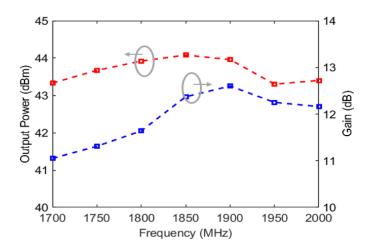

| 5.20 | Measured saturated power and small signal gain versus frequency for           |    |

|      | CW signal                                                                     | 85 |

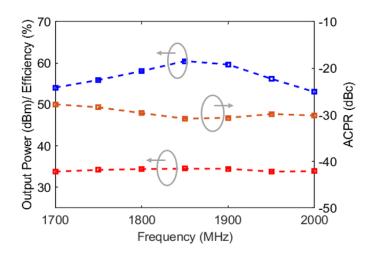

| 5.21 | Measured average power, efficiency and ACPR for modulated signal              | 86 |

# Figure

| ure  |                                                                  | Page |

|------|------------------------------------------------------------------|------|

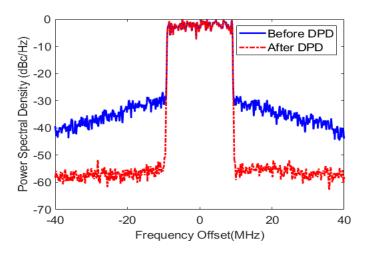

| 5.22 | Measured power spectral density with modulated signal before and |      |

|      | after DPD                                                        | 86   |

## Chapter 1

#### INTRODUCTION

Figure 1.1: Active vs Passive Antenna

With the rapid proliferation of the modern cellular communication networks, 5G/5G+ networks are employing active antenna systems (AAS) to improve the enduser experience, capacity, and coverage. These systems use powerful techniques such as state-of-the-art beamforming and multiple-input multiple-output (MIMO) architectures. In passive antenna systems, the Remote Radio Unit (RRU) and the passive components (antenna) are independent components, whereas in AAS, the RRU and antenna elements are integrated in a single radio unit, as illustrated in Figure 1.1. By putting the antennas near to or integrated with the RF modules, the AAS improves the communication throughput and reduces power consumption as well as cable loss. There is also a growing demand to reduce the weight of these AAS-based radio units for simplified installation, reduced tower loading, and improved tower utilization. Since power amplifiers (PAs) are the most power-hungry block in a radio transceiver,

| <b>m</b> 11 | 1 1          |

|-------------|--------------|

| Table       |              |

| Table       | <b>T • T</b> |

| Class | $I_{dq}$                 | Conduction      | Efficiency %          |

|-------|--------------------------|-----------------|-----------------------|

|       |                          | Angle           |                       |

| A     | $\frac{I_{max}}{2}$      | $2\pi$          | 50 %                  |

| AB    | 0 to $\frac{I_{max}}{2}$ | $\pi$ to $2\pi$ | 50% to $78.54%$       |

| В     | 0                        | π               | 78.54 %               |

| С     | 0                        | 0 to $\pi$      | 78.54 $\%$ to $100\%$ |

**Basic PA Classes**

there is a growing need for the development of high efficiency RF power amplifiers (PAs) with compact footprint to meet these stringent AAS requirements. These PAs should be invented to enable higher level of integration and reduction in radio unit size/weight/cost, while also increasing network capacity.

Figure 1.2: (a) Normalized fourier current components, (b) normalized power with respect to class-A, and (c) Efficiency for different classes of operation

#### Background

Linear RF PAs can be generally divided into four classes of operation based on the PA's bias condition. The main classes are class-A, class-B, class-AB and class-C. In the discussion of these basic classes of operation, it's assumed that the higher order harmonics are short-circuited in the current generator plane. This short circuited harmonic condition is also dubbed as "tuned class-B" operation for simplification. Table 1.1 shows quiescent current  $(I_{dq})$ , conduction angle and efficiency for different classes of PA operation. In Figure 1.2, the normalized Fourier current, power, and efficiency are plotted with respect to conduction angle. As conduction angle decreases from class-A to class-C, efficiency goes up, while linearity degrades. Therefore, a strong trade-off between efficiency and linearity exists in these classes of operation. To improve the efficiency and to relax the efficiency-linearity trade-off, advanced PA design techniques are required.

Efficiency improvement techniques can be divided into two major categories. In the first category, the higher order harmonics are manipulated to engineer the voltage and/or current waveforms to improve the PA's performance. These kind of PAs are generally called harmonic tuned PAs. Harmonic tuned PAs were originally targeted for saturated PA operation. When a PA becomes saturated, higher order harmonics are abundantly generated and voltage /current waveforms can be significantly engineered by controlling their harmonics. However, in harmonic tuned PAs, very stringent fundamental and higher order harmonic load conditions need to be imposed, which can be a challenge for practical applications. To circumvent this limitation, the idea of continuous-mode PAs was introduced. Continuous-mode PAs can achieve the same high performance as basic harmonic tuned PAs while allowing more flexibility in impedance conditions. The second category of efficiency improvement techniques is focused on output power backoff (OBO) operation. Envelope Elimination and Restoration (EER), Envelope Tracking (ET), Linear Amplification using Non-linear Component (LINC), Doherty Power Amplifiers (DPA), Polar Transmitters, etc. are some of the techniques that fall into this category. For these techniques, a 'tuned

Figure 1.3: Simple PA output model

class-B" operation is generally assumed, which means that only the fundamental components are considered and higher order harmonics are short-circuited (negligible). In these architectures, one or more PAs are utilized and load impedance and/or bias voltage is modulated with respect to power level to improve the overall PA's performance. Among these architectures, DPAs are widely used in cellular infrastructure applications due to their simple configuration with high output back-off efficiency. They do not require fast switching regulators to track the envelope signal like ET amplifiers or very stringent phase accuracy required in a LINC amplifier. Moreover, these other architectures also need complicated DPD algorithms for linearization, which is typically not required for DPAs. Because of these inherent architectural advantages, DPAs have become the most popular choice for cellular infrastructure applications. As this thesis is focused on applications for cellular infrastructure, the discussion on OBO efficiency improvement will be limited to DPAs.

In the next section, the fundamental ideas behind harmonic tuned PAs and continuous-mode PAs will be discussed in detail. In the subsequent section, the DPA operating principle is introduced. In DPA operation, the carrier amplifier becomes moderately compressed/saturated at OBO at the on-set of peaking amplifier turning on. Hence, by combining harmonic tuned/continuous-mode techniques with the DPA

Figure 1.4: Ideal class-F (a) voltage, (b) current, and (c) impedance locations on smith chart

architecture, the OBO efficiency can be further improved. This will be demonstrated in one of the works presented in this dissertation.

#### 1.0.1 Harmonic Tuned and Continuous-mode PA Operation

Compared to class-B/AB amplifiers, harmonic tuned PAs offer better performance (e.g. higher efficiency, power and gain). This can be achieved by providing specific impedance terminations for fundamental and higher order of harmonics to control/shape the drain-source voltage and current waveforms. Theoretically, an infinite number of harmonic terminations are required to achieve the best performance. However, in practice, only a finite number of harmonic controls are possible. Figure 1.3 illustrates a simple PA output model with fundamental impedance matching and harmonic trapping network that would realize certain chosen impedance conditions at the intrinsic current generator plane. There are three main harmonic tuned operations: class-F, class-F<sup>-1</sup> and class-J. Their detailed operating principles are described below.

Figure 1.5: Ideal class- $F^{-1}$  (a) current, (b) voltage, and (c) impedance locations on smith chart

#### Class-F

In a class-F PA, the even-order harmonics are terminated as short circuits and the odd-order harmonics are terminated as open circuits in the current generator plane. The voltage waveform is engineered and with a class-B bias condition (conduction angle of  $\pi$ ), the PA results in a square voltage waveform and half-rectified current waveform. Voltage and current waveforms contain only odd and even order harmonics, respectively. The ideal voltage and current waveforms and the impedance locations for class-F operation are shown in Figure 1.4. Ideally, infinite number of harmonics need to be terminated for class-F operation. However, in reality, only  $2f_0$  and  $3f_0$  can be controlled. With  $2f_0-3f_0$  terminated, the time-domain voltage and current for class-F operation can be expressed as (1.1) and (1.2), where  $\theta = 2\pi f_0 t$ . A  $2f_0-3f_0$  class-F PA can ideally achieve 90.69 % efficiency.

$$v_{ds,classF} = V_{dd} (1 - \frac{2}{\sqrt{3}} \cos(\theta) + \frac{1}{3\sqrt{3}} \cos(3\theta))$$

(1.1)

$$i_{ds,classF} = I_{max}(\frac{1}{\pi} + \frac{1}{2}\cos(\theta) + \frac{2}{3\pi}\cos(2\theta))$$

(1.2)

Figure 1.6:  $f_0$  (black) and  $2f_0$  (red) impedance locations on smith chart for (a) class-B, (b) class-J, and (c) voltage and current waveforms for class-J

## $Class-F^{-1}$

A class- $F^{-1}$  PA is the dual (often called inverse) of a class-F PA. In class- $F^{-1}$ , the oddorder harmonics are terminated as short circuits and the even-order harmonics are terminated as open circuits in the current generator plane. Considering class-B bias condition (conduction angle of  $\pi$ ), the PA results in a square current waveform and half-rectified voltage waveform. Voltage and current waveforms contain only even and odd order harmonic components, respectively. The ideal voltage and current waveforms and the impedance locations for class- $F^{-1}$  operation are shown in Figure 1.5. Similar to class-F, only  $2f_0$  and  $3f_0$  control is feasible for class- $F^{-1}$  PAs. With harmonic controls being limited to  $2f_0$  and  $3f_0$ , the voltage and current waveforms for class- $F^{-1}$  operation can be expressed as (1.3) and (1.4), where  $\theta = 2\pi f_0 t$ . A  $2f_0$ - $3f_0$ class- $F^{-1}$  PA can ideally achieve 81.69 % efficiency.

$$v_{ds,classF^{-1}} = V_{dd}(1 + \sqrt{2}cos(\theta) + \frac{1}{2}cos(2\theta))$$

(1.3)

$$i_{ds,classF^{-1}} = I_{max}(0.3676 - 0.4246\cos(\theta) + 0.0707\cos(3\theta))$$

(1.4)

#### Class-J

The idea of engineering the class-B voltage waveform and achieving the same performance as class-B with different load conditions was first introduced by Cripps [1]. This class of harmonic tuned PA operation is called class-J. Instead of a short-circuit  $2f_0$  load condition as in class-B, in class-J operation, the  $2f_0$  load is terminated in the inductive region. At the same time, the  $f_0$  load is terminated in the capacitive region. This results in voltage peaking and partial overlap between voltage and current waveforms. However, the power and efficiency remain the same as class-B. Class-J produces the same 78.54 % theoretical efficiency as a class-B PA. The impedance locations on the smith chart and voltage and current waveforms are plotted in Figure 1.6. Time domain voltage and current expressions for class-J operation can be found in (1.5) and (1.6).

$$v_{ds,classJ} = V_{dd}(1 - \cos(\theta))(1 - \sin(\theta))$$

(1.5)

$$i_{ds,classJ} = I_{max}(\frac{1}{\pi} + \frac{1}{2}\cos(\theta) + \frac{2}{3\pi}\cos(2\theta))$$

(1.6)

From class-J operation, it's evident that for harmonic tuned operation, harmonics do not need to be strictly at short/open circuit regions. This finding expands the design space for PAs and allows for more PA design flexibility and maximized PA performance when designing with practical limitations of active (power) devices and passive structures. Expanding upon this idea, Cripps and other PA researchers established the continuous mode theory. There can be many solutions for fundamental and harmonic load conditions that can produce the same performance. There are three main continuous mode operations: class-BJ/continuous class-J, continuous class-F (CCF) mode and continuous class- $F^{-1}$  (CCF<sup>-1</sup>) mode.

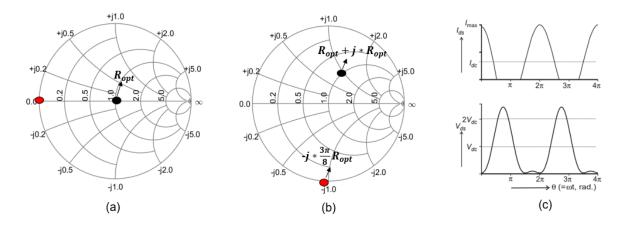

Figure 1.7: Class-BJ (a) voltage and current waveforms, (b) impedance locations on smith chart

#### Class-BJ/continuous class-J

In class-BJ operation, the time domain class-B voltage waveform is multiplied by  $1 - \alpha sin(\theta)$ , where  $\alpha$  is called the continuous mode parameter, and included in (1.7). This creates a series of voltage waveforms and the design space is expanded. The current waveform remains unchanged, as shown in (1.8). The current and voltage waveforms for class-BJ operation are plotted in Figure 1.7 (a). Each voltage waveform represents a pair of fundamental and second harmonic impedances on the smith chart, which are shown in Figure 1.7 (b).

$$v_{ds,classBJ} = V_{dd}(1 - \cos(\theta))(1 - \alpha \sin(\theta)), \quad -1 \le \alpha \le 1$$

(1.7)

$$i_{ds,classBJ} = I_{max}(\frac{1}{\pi} + \frac{1}{2}\cos(\theta) + \frac{2}{3\pi}\cos(2\theta))$$

(1.8)

#### Continuous class-F (CCF) mode

In CCF operation, the time domain class-F voltage waveform is multiplied by  $1 - \alpha sin(\theta)$ , as shown in (1.9). Similar to class-BJ, this creates a series of voltage wave-

Figure 1.8: CCF (a) voltage and current waveforms, (b) impedance locations on smith chart

forms and the design space is expanded. The current waveform remains half-rectified, as presented in (1.10). The current and voltage waveforms for CCF operation are plotted in Figure 1.8 (a). Each voltage waveform represents a pair of fundamental and second harmonic impedances on the smith chart, which are shown in Figure 1.8 (b).

$$v_{ds,CCF} = V_{dd} (1 - \frac{2}{\sqrt{3}}\cos(\theta) + \frac{1}{3\sqrt{3}}\cos(3\theta))(1 - \alpha\sin\theta), \quad -1 \le \alpha \le 1$$

(1.9)

$$i_{ds,CCF} = I_{max}(\frac{1}{\pi} + \frac{1}{2}\cos(\theta) + \frac{2}{3\pi}\cos(2\theta))$$

(1.10)

# Continuous class- $F^{-1}$ (CCF<sup>-1</sup>) mode

Unlike class-BJ and CCF, in CCF<sup>-1</sup> operation, the time domain class-F<sup>-1</sup> current waveform is multiplied by  $1 - \alpha sin(\theta)$ , as shown in (1.12). This creates a series of current waveforms and the design space is expanded. The voltage waveform remains half-rectified, as presented in (1.11). The current and voltage waveforms for CCF<sup>-1</sup> operation are plotted in Figure 1.9 (a). Each current waveform represents a pair of fundamental and second harmonic impedances on the smith chart, which are shown

Figure 1.9:  $CCF^{-1}$  (a) voltage and current waveforms, (b) impedance locations on smith chart

Figure 1.10: (a) Normalized output power, and (b) efficiency for all continuous mode PAs

in 1.9 (b).

$$v_{ds,CCF^{-1}} = V_{dd}(1 - \cos(\theta))$$

$$i_{ds,CCF^{-1}} = I_{max}(0.3676 - 0.4246\cos(\theta) + 0.0707\cos(3\theta))(1 - \alpha\sin\theta), \quad -1 \le \alpha \le 1$$

$$(1.12)$$

Normalized output power and efficiency for different continuous mode PAs with

Figure 1.11: (a) A DPA block diagram, and (b) a simplified current source model of a DPA

respect to  $\alpha$  are plotted in Figure 1.10. It's evident that ideally with the variation of  $\alpha$ , power and efficiency remain constant in continuous mode PAs. This allows for enhanced design flexibility.

#### 1.0.2 Fundamental Operation of the Doherty Power Amplifier

Invented in 1936 by William H. Doherty, Doherty amplifiers gained popularity in the mid-2000s as the preferred PA choice for cellular infrastructure. This choice was motivated by the DPA's higher efficiency at high power back-off level. Currently in cellular base-stations (BTS), only Doherty amplifiers are being used for power amplification. Figure 1.11 (a) depicts a block diagram of a DPA. There are two amplifiers involved: the carrier amplifier and the peaking amplifier. Generally, the carrier amplifier is biased in class-B/AB and the peaking amplifier is biased in class-C. The DPA's behavior is a function of input power and is divided into two regions: saturation when both devices are supplying their maximum power, and back-off power when the peaking device is turned off and only the carrier amplifier is producing power. For a symmetric Doherty PA in which the carrier and peaking amplifiers are of the same size, the break point between this saturation and back-off level happens at a power level 6dB before (lower) than the saturation point. For the Doherty to be ef-

Figure 1.12: DPA efficiency with respect to normalized output voltage for different power ratio

fective, the real part of the output impedance at the intrinsic current generator plane of the carrier amplifier needs to have a high impedance before the break-point. At saturation, both amplifiers should see the optimum impedance for maximum power generation. Thus, when the input power changes from low to high power, the output combiner allows for load modulation of the output impedance of the carrier and auxiliary amplifiers. The Doherty is therefore referred to as a load-modulation technique.

Figure 1.11 (b) shows a simple current source model of the DPA with output combiner.  $I_1$  and  $I_2$  represent carrier and peaking amplifiers, respectively. The different impedances at the current source plane and the combiner planes, as annotated in Figure 1.11 (b), can be expressed as:

$$Z_{1}^{'} = \frac{R_{L}}{2} \left(\frac{I_{1}^{'} + I_{2}}{I_{1}^{'}}\right) \tag{1.13}$$

$$Z_1 = \frac{R_L^2}{Z_1'} \tag{1.14}$$

$$Z_{2}^{'} = \frac{R_{L}}{2} \left(\frac{I_{1}^{'} + I_{2}}{I_{2}}\right) \tag{1.15}$$

DPA efficiency with respect to normalized output voltage  $(V_o/V_{om})$  is plotted in

Figure 1.13: 3-way DPA, (a)block diagram, and (b) efficiency for different power ratio

Figure 1.12. Class-B amplifier efficiency is also with respect to normalized PA output power is given in the same plot. The plot demonstrates that efficiency for the class-B PA is poor at the OBO condition, which makes it unsuitable for modulated signals with variable envelope (power). By utilizing load modulation, DPAs can achieve additional efficiency peaking at OBO and thus drastically improve PA performance from a class-B configuration. For conventional DPAs, the efficiency peaking at OBO is a function of peaking to carrier power ratio (r). OBO range can be extended by increasing the asymmetry (r). The PDF of an unclipped WCDMA test model (pink) is also plotted on Figure 1.12. To get the optimum efficiency peaking at back-off is aligned with the maxima of the PDF of the modulated signal in use. With the symmetric configuration (r=1) efficiency peaking happens at  $V_o/V_{om}=0.5$  or at 6 dB OBO. An asymmetric configuration (r>1) is thus generally required to get the best performance with high PAPR modulated signals that are used in cellular infrastructure.

Multi-way or multi-stage DPAs are used to further extend the DPA efficiency range. Instead of using one carrier and one peaking amplifier as in a 2-way DPA, multi-way DPAs include more than one peaking amplifier to introduce multiple peaks at back-off powers. For example, a 3-way DPA block diagram is presented in Figure 1.13 (a).  $r_1$  represents the power ratio between the first peaking PA and carrier PA, and  $r_2$  represents the ratio between the second peaking PA and carrier PA. the efficiency plot of a 3-way DPA with respect to power back-off (dB) is plotted in Figure 1.13 (b). There are two efficiency peaks in the back-off region. By controlling the two power ratios ( $r_1$  and  $r_2$ ), the locations of the efficiency peaks can be controlled/chosen.

These conventional two-way and multi-way architectures suffer from some direct trade-offs between different design parameters. Moreover, the ideal harmonic tuned and continuous mode PA theories that were discussed earlier do not take into account some of the inherent non-linearities (and non-idealities) present in a real transistor. It's important to address these issues in a detailed mathematical manner to understand the nature of the limiting factors and innovate refined architectures to circumvent these practical implementation issues. It's also important, especially for 5G+ applications, to develop compact PA and combiner architectures that allow for a reduced overall DPA footprint.

#### 1.1 Organization of the Work

This dissertation includes four power amplifiers (PAs) that demonstrate state-ofthe art performance for wireless communication infrastructure, as they focus on the improvement of efficiency and reduction of the PA's physical footprint. The organization of the following chapters is as follows. In Chapter 2, a detailed mathematical analysis of non-linear  $C_{ds}$  effect is presented for continuous mode class-F (CCF) PAs. From mathematical analysis, it is shown that by utilizing the non-linearity of  $C_{ds}$ , the PA performance can be enhanced in certain operating conditions compared to ideal CCF operation. Chapter 3 presents a design approach used to realize a highly efficient Gallium Nitride (GaN) based class-J Doherty Power Amplifier (DPA), delivering +45 dBm peak power at 3.5 GHz, which supports 5G mMIMO small-cell infrastructure transmitters. The DPA is implemented in a compact form factor with all circuitry, excluding the output combiner and input splitter, placed in a 7 mm x 7 mm quadflat no-leads (QFN) plastic encapsulated package. A circuit topology is presented to realize the class-J network inside the package, including the non-linearity of  $C_{ds}$  for enhanced performance.

In Chapter 4, a compact output combining network for a packaged integrated asymmetric DPA is presented. A new method is introduced for the combining network that absorbs part of the peaking amplifier's  $C_{ds}$  into the impedance transformer, thus extending the C-L-C based " $C_{ds}$  absorption" technique to asymmetric DPAs. Based on the proposed combining network, a two-stage LDMOS integrated asymmetric DPA was designed, fabricated, and measured for a 2.6 GHz band of operation.

In Chapter 5, a novel extended back-off efficiency range Doherty power amplifier (DPA) is presented that engineers the mutual interaction between peaking off-state impedance and combining load impedance. A generic analysis to establish the theory of operation shows that unique closed form relationship can be established between peaking off-state impedance and combining load impedance. Compared to prior extended back-off Doherty works, the proposed theory introduces an expanded design space that renders flexibility to incorporate multiple frequency points to improve the bandwidth performance. Moreover, the generic analysis also covers any arbitrary combining approach suitable for both symmetric and asymmetric configurations. To corroborate the theory, a proof-of-concept prototype DPA with an asymmetric configuration was designed using commercially available packaged Gallium Nitride (GaN) High-Electron-Mobility Transistors (HEMT) for 1.7-2 GHz operation.

#### Chapter 2

# NON-LINEAR $C_{DS}$ EFFECT ON CONTINUOUS CLASS-F MODE POWER AMPLIFIERS

#### 2.1 Introduction

Figure 2.1: Fundamental and harmonic locations for (a) class-B PA, and (b) class-BJ PA

Parasitic capacitances such as drain-source capacitance  $(C_{ds})$ , gate-source capacitance  $(C_{gs})$  and gate-drain capacitance  $(C_{gd})$  are always present in a real transistor. Ideal PA theories targeted for harmonic tuned power amplifiers have been developed using the current-generator plane of a transistor, without taking these parasitic capacitances into account. However, if these parasitic capacitances possess linear behavior, they can be easily de-embedded to get access to the current-generator plane for establishing the ideal high performance condition, which is what is performed in most design techniques. However, for many devices, these parasitic capacitances show significant non-linearity that cannot be ignored. This is especially prominent with the effect of  $C_{ds}$  non-linearity on continuous mode power amplifiers, and with the high nonlinearity of  $C_{ds}$  in gallium nitride (GaN) and LDMOS devices. The motivation of this work is to mathematically analyze the effect of non-linear  $C_{ds}$  on the operation of continuous class-F (CCF) mode PA operation, which provides design insight and a new set of design constraints to achieve optimized CCF performance.

In a class-B amplifier, the conduction angle of the amplifier is  $\pi$  and the fundamental impedance is  $R_{opt}$ , where

$$R_{opt} = \frac{2V_{dd}}{I_{max}} \tag{2.1}$$

Here,  $V_{dd}$  and  $I_{max}$  are the drain supply voltage and maximum current of the amplifier, respectively. All the higher order harmonics are assumed to be short circuited in a class-B PA. Extending the design space of class-B amplifiers was first introduced in [1] through the invention of the class-BJ amplifier. Figure 2.1 shows the location of fundamental and harmonic impedances for class-B and class-BJ PAs. Following with a similar approach, continuous class-F (CCF) mode PAs were architected to extend the conventional class-F design space [2]. The CCF theory introduces the idea that a short second harmonic and an open third harmonic condition for a conventional class-F PA is not a unique solution. Rather, an extended design space exists where the same high performance (efficiency and power) of a conventional class-F PA is achieved. Conventional class-F operation is narrowband due to the requirement of short and open impedance terminations at second and third harmonics, whereas an extended design space of CCF PAs facilitates wideband operation. In [3], a wideband PA with 74% efficiency was reported to prove the theory introduced in [2].

The original theory of class-BJ PAs does not take into account the non-linearity introduced by device drain-source capacitance,  $C_{ds}$  [1]. Recently published work shows that in the presence of non-linear  $C_{ds}$ , the design space of a class-BJ PA deviates from

Figure 2.2: (a) Impedance locations for ideal CCF mode, and (b) CCF voltage and current waveforms original theory, and the power and efficiency predicted by the class-BJ theory does not apply over the entire design space [4]. in this work, CCF PAs are mathematically analyzed for the first time to demonstrate the effects of non-linear  $C_{ds}$ . The analysis provides design insight and constraints to achieve optimized CCF PA performance in the presence of non-linear  $C_{ds}$ .

#### 2.2 Theory of CCF PAs

CCF mode is an extended design space of class-F PAs first introduced in [2]. The theory suggests a single-solution open circuit third harmonic condition, whereas the second harmonic short circuit condition is but one and not the only solution to CCF operation. The voltage waveform for CCF mode can be expressed as [1]:

$$v_{ds}(\alpha) = V_{dd}\left(1 - \frac{2}{\sqrt{3}}\cos(\theta) + \frac{1}{3\sqrt{3}}\cos(3\theta)\right)\left(1 - \alpha\sin\theta\right)$$

(2.2)

where  $\theta = 2\pi f_0 t$ ,  $f_0$  is the fundamental frequency, and  $\alpha$  is the continuous mode parameter,  $-1 \leq \alpha \leq 1$ . If the current waveform is considered half rectified, which is the usual assumption for a tuned class-B bias condition, then the current can be expressed as:

$$i_{ds} = I_{max}(\frac{1}{\pi} + \frac{1}{2}\cos(\theta) + \frac{2}{3\pi}\cos(2\theta))$$

(2.3)

For each  $\alpha$  value, from (2.3) and (2.3), there can be found a pair of fundamental  $(f_0)$  and second harmonic  $(2f_0)$  voltage components that constitute a mode for CCF operation. The third harmonic component  $(3f_0)$  always remains an open circuit. For narrowband applications, a designer has the freedom to choose any  $\alpha$  value. For wideband applications, a range of  $\alpha$  values can be chosen so that the  $f_0$  and  $2f_0$  impedances synthesized by the matching network over the target frequency band follow the impedance trajectories dictated by  $\alpha$ . The impedance locations and the voltage and current waveforms for CCF mode are plotted in Figure 2.2.

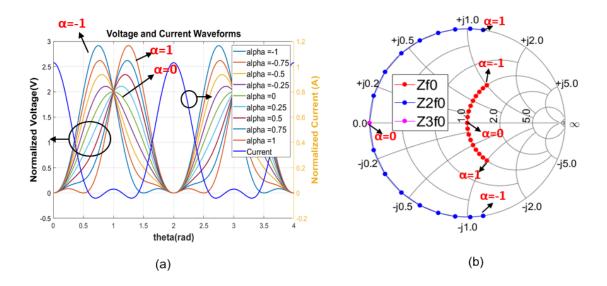

## 2.3 Effect of Non-linear $C_{ds}$ on CCF Mode PAs

The ideal CCF mode that was described in Section II is based on the assumption that  $C_{ds}$  is linear in nature, e.g.,  $C_{ds}$  stays constant with drain voltage variation. However, in real devices,  $C_{ds}$  does not stay constant, but rather exhibits non-linearity with strong dependence on drain voltage. For some devices, the non-linearity is relatively weak and can be approximated with linear capacitors. But in most power devices of interest (LDMOS and GaN), the capacitive non-linearity is too strong to be ignored. In this section, a mathematical analysis is presented that illustrates the effect of non-linear  $C_{ds}$  on fundamental and second harmonic impedance trajectories for CCF operation. The analysis also shows the impact on key RF PA metrics. NXP's 50V LDMOS device is used for demonstration. In general, a non-linear  $C_{ds}$  behavior can be represented by the following expression [4]:

$$C_{ds}(v_{ds}) = C_{off} + \frac{C_0}{(1 + \frac{v_{ds}}{v_0})^m}$$

(2.4)

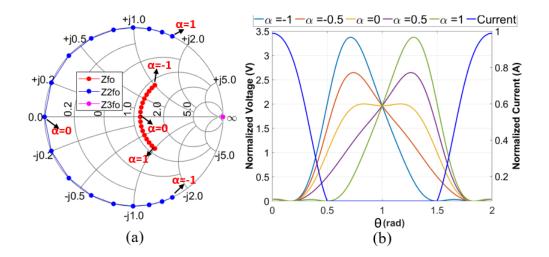

Figure 2.3: (a) Capacitance versus drain voltage for non-linear  $C_{ds}$  with various fitting parameters, (b) simplified equivalent circuit model of the PA device under operation, (c) calculated time domain voltage and current waveforms for  $-1 \le \alpha \le 1$  at the LDP for CCF mode

where  $C_{off}$ ,  $C_0$ ,  $v_0$ , and m are general fitting parameters, which are extracted for a given technology. As an example, Figure 2.3(a) illustrates non-linear  $C_{ds}$  behavior for different values of fitting parameters.  $C_0$  and  $C_{off}$  define the capacitance at low voltage and high voltage regions, respectively. Parameters  $v_0$  and m control the slope of the capacitance curve from high to low values of  $V_{ds}$ . In this analysis, the parameter values are chosen as  $C_{off}=0.8$  pF,  $C_0=5.5$  pF,  $v_0=11$  V and m=2, which are representative of the selected NXP device. The RF PA is assumed to operate with  $V_{dd} = 48$  V,  $I_{max} = 1$  A, and  $f_0 = 1$  GHz. To analyze the impact of the non-linear  $C_{ds}$  on CCF operation, a simplified equivalent circuit model is presented that includes lossless non-linear  $C_{ds}$  in parallel with a current source,  $i_{ds}$  (Figure 2.3(b)). A linear de-embedding methodology is employed by placing a negative linear capacitor,  $C_{const}$ , in parallel with the non-linear  $C_{ds}$  [4]. In this example,  $C_{const}$  is 1.19 pF. The currents  $i_{cds}$  and  $i_{const}$  are not equal, as the negative capacitance does not fully cancel out non-linear  $C_{ds}$  and some residual current flows in the circuit. Applying KCL to the equivalent circuit model in Figure 2.3(b), the load current,  $i_{load}$ , can be expressed as in (2.5).

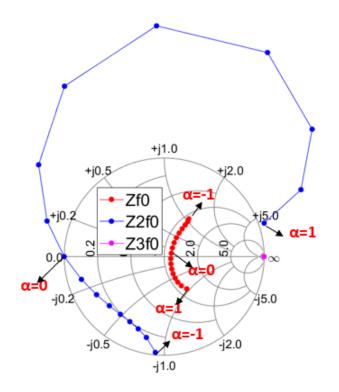

Figure 2.4:  $f_0$ ,  $2f_0$ , and  $3f_0$  impedance trajectories at the LDP

As illustrated in Figure Figure 2.3(b), an open circuit third harmonic load impedance condition is imposed at the linear de-embedding plane (LDP) per CCF theory, thus forcing the load current component,  $i_{load,3f0}$ , to be zero. The open circuit third harmonic is assumed to be realized by output matching circuitry. Substituting (2.4) into (2.5) for  $C_{ds}$ , the time domain load current is obtained as a function of  $\alpha$ . The calculated time-domain load current and voltage are plotted in Figure Figure 2.3(c). Out of phase fundamental and second harmonic reactive currents are generated because of the varactor effect from non-linear  $C_{ds}$ . These out of phase components distort the ideal current waveform (see Figure 2.3(c)). By performing a Fast Fourier Transform (FFT) on the time-domain voltage and current waveforms, the fundamental and harmonic load impedances are calculated at the LDP, and Figure 2.4 portrays the newly calculated impedance trajectories. In  $-1 \leq \alpha \leq 0$  range, the  $2f_0$  impedances remain inside the smith chart ( $\Gamma_{2f0} < 1$ ). Hence, power needs to be dissipated at  $2f_0$  frequency to satisfy those impedance conditions. On the other hand, for  $0 < \alpha \leq 1$ , the trend is opposite and  $2f_0$  impedances are such that  $\Gamma_{2f0} > 1$ , meaning that power must be injected from an external  $2f_0$  source. These overall trends for  $2f_0$  impedances have similarities to that reported for a class-BJ with non-linear  $C_{ds}$ [4]. However, an important difference in the class-BJ amplifier is that  $2f_0$  impedances are not impacted by non-linear  $C_{ds}$  at  $\alpha = -1$  and  $\alpha = 1$ . In CCF mode, the  $\alpha = -1$ and  $\alpha = 1$  impedances are impacted, as the  $2f_0$  impedances at those points remain inside and stay outside the smith chart, respectively.

The power at  $f_0$  and  $2f_0$  ( $P_{f0}$  and  $P_{2f0}$ ) and the efficiency are calculated from (2.6)-(2.8) based on the fourier components of the voltage and current waveforms. In Figure 2.5(a),  $P_{f0}$  and  $P_{2f0}$  are plotted as  $\alpha$  is varied from -1 to 1. Conventional CCF theory (linear  $C_{ds}$ ) suggests that  $P_{f0}$  should remain constant and  $P_{2f0}$  should be zero for all values of  $\alpha$ . However, the effect of non-linear  $C_{ds}$  for  $-1 \leq \alpha \leq 0$  range illustrates that  $P_{f0}$  has a lower value and  $P_{2f0}$  is greater than zero. This indicates energy upconversion, as energy gets transferred from the fundamental to the second harmonic due to the non-linear capacitance. Conversely, for  $0 < \alpha \leq 1$ ,  $P_{2f0}$  is less than zero and  $P_{f0}$  is higher than the linear  $C_{ds}$  approximation, indicating downconversion from the second harmonic to fundamental frequency. The efficiency in Figure 2.5(b) follows the same trend as  $P_{f0}$ .

$$i_{load}(\alpha) = -i_{ds} - \frac{dv_{ds}(\alpha)}{dt} (C_{ds}(v_{ds}) - C_{const})$$

(2.5)

$$P_{f0} = 0.5 * Re(v_{ds,f0} * conj(i_{load,f0}))$$

(2.6)

$$P_{2f0} = 0.5 * Re(v_{ds,2f0} * conj(i_{load,2f0}))$$

(2.7)

$$Efficiency = \frac{P_{f0}}{P_{dc}} * 100\% = \frac{P_{f0}}{v_{ds,dc}i_{load,dc}} * 100\%$$

(2.8)

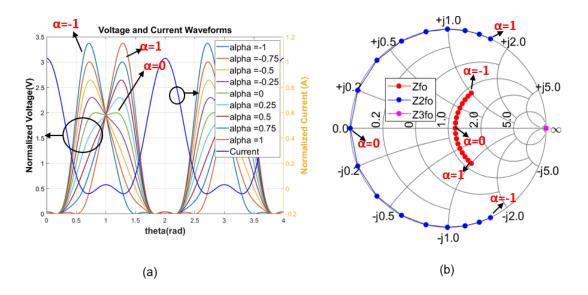

The calculated power and efficiency in Figure 2.5 provide critical insight for CCF

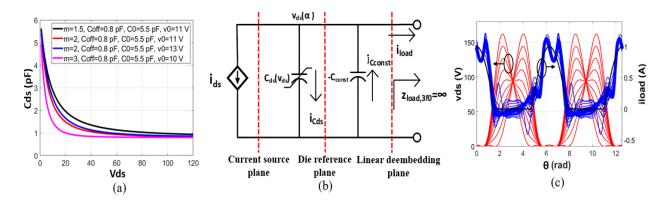

Figure 2.5: (a) Calculated  $f_0$  and  $2f_0$  power, (b) calculated efficiency

PA design. For example, to obtain higher power and efficiency, a design space of  $0 < \alpha \leq 1$  leads to improvements in both power and efficiency, where the theoretical efficiency reaches as high as 100% at  $\alpha = 0.75$ . However, external  $2f_0$  power injection is required in this range, which adds complexity and assumed dc power consumption. Another solution of interest requires that  $2f_0$  impedances remain at  $\Gamma_{2f0} = 1$  for values of  $-1 \leq \alpha \leq 1$ , thus corresponding to passive second harmonic terminations. To impose this condition at  $2f_0$ , a phase shift parameter  $\phi$  needs to be introduced in the voltage expression [4]. With proper choice of  $\phi$ , new  $2f_0$  reactive voltage components are generated that counteract the effect of the  $2f_0$  reactive currents generated by

Figure 2.6: (a) Phase shift  $\phi$  vs alpha, (b) Impedance trajectories after  $\phi$  is applied

non-linear  $C_{ds}$ . By inserting phase shift parameter  $\phi$  in the voltage expression, the new drain-source voltage expression become,

$$v_{ds}(\alpha) = V_{dd}(1 - \frac{2}{\sqrt{3}}\cos(\theta + \phi) + \frac{1}{3\sqrt{3}}\cos(3\theta + 3\phi)).(1 - \alpha\sin(\theta + \phi))$$

(2.9)

While it's a cumbersome process to identify values of  $\phi$  that satisfies  $\Gamma_{2f0} = 1$ from closed form expressions, correct  $\phi$  values can be solved easily using an iterative method. Making an initial assumption that  $\phi$  should always be within  $\pm \pi/2$ ,  $\phi$ is swept from  $-\pi/2$  to  $\pi/2$  as  $\alpha$  is varied. For each value of  $\alpha$ , the real part of  $Z_{2f0}$  is calculated using (2.4), (2.5), and (2.9) using FFT. The correct  $\phi$  value is identified that forces  $Re(Z_{2f0})$  to zero. Results for the numerical evaluation with

Figure 2.7: (a) Power before and after phase shift, and (b) efficiency before and after phase shift

$-1 \leq \alpha \leq 1$  calculated in 0.125 steps are given in Figure 2.6(a). Figure 2.6(b) shows the trajectory of the load impedances after the  $\phi$  values are applied, where  $2f_0$  load trajectories now stay at the edge of the smith chart for the full  $\alpha$  range. This indicates that only passive termination can realize this solution without the need for  $2f_0$  power dissipation or injection. However, the  $2f_0$  load trajectory has a clockwise rotation from its original location in Figure 2.2(a) when assuming linear  $C_{ds}$ . Similarly, the  $f_0$ load trajectory of Figure 2.6(b) diverges from its original trajectory in Figure 2.2(a). The power and efficiency after introducing phase shift are calculated from (2.6)-(2.8), once  $\phi$  is determined and plotted in Figure 2.6(a). There is a reversal in power and efficiency trends from the previous solution with no phase shift (see Figure 2.7). In the  $-0.875 \leq \alpha \leq -0.625$  range, power and efficiency go above their nominal (ideal) values, thus suggesting a targeted operation design space. These higher power and efficiencies are not achievable in this range without applying  $\phi$ .

# 2.4 Summary

The mathematical analysis presented in this work concludes that the constant power and efficiency predicted by CCF PA theory does not stay constant in the presence of a non-linear  $C_{ds}$ . From analysis, two possible CCF PA solutions are presented to optimize performance. The first solution requires external second harmonic power to be injected at the output in  $0 < \alpha \leq 1$  range for high performance. The second solution with passive second harmonic termination may achieve higher than nominal (linear  $C_{ds}$ ) performance by targeting the  $-0.875 \leq \alpha \leq -0.625$  range. The presented methodology can be used for any device technology that possesses non-linear  $C_{ds}$ , and provides design guidance for choosing the optimal  $f_0$  and  $2f_0$  impedances in CCF PAs with the presence of non-linear  $C_{ds}$ .

## Chapter 3

# A HIGH PERFORMANCE CLASS-J DOHERTY POWER AMPLIFIER

## 3.1 Introduction

The Doherty Power Amplifier (DPA) has become widely adopted for cellular infrastructure transmitters, as it is well suited to achieve high efficiencies when amplifying multi-carrier signals with large peak to average power ratios (PAPR). DPAs have a typical operating condition at 8 dB OBO, and it is critical to maximize efficiency and linearity at this back-off level. Furthermore, the DPA must be amenable to DPD linearization, which entails careful attention to numerous design details, such as minimizing amplitude (AM-AM) and amplitude to phase (AM-PM) excursions to acceptable levels, and implementing low impedance baseband terminations, especially at the device's drain terminal. Due to the use of many transmitter pipes in a mMIMO system, package size and space are quite limited and it becomes necessary to realize the DPA in a small and cost effective form factor. This is particularly difficult in a DPA given that the architecture uses both carrier and peaking sub-amplifiers and requires matching circuity associated with each. This work utilizes integrated passive device (IPD) technology, whereby input and output pre-matching circuitry as well as harmonic termination networks are realized as lumped elements (e.g. spiral inductors, MIM caps) on a low-cost silicon (Si) integrated circuit (IC) technology. The DPA device is then realized in a small form factor QFN package consisting of wire bond interconnects between several Si ICs, GaN devices, and package leads.

A Class-J amplifier topology [8], [25] is chosen for the Doherty's carrier subamplifier because of its simple required drain harmonic termination and high efficiency

Figure 3.1: Class-B/J fundamental (red) and second harmonic (blue) load impedance at intrinsic device plane (linear  $C_{ds}$ ), and (green) enhanced efficiency region of  $\alpha$  reported in [4] for non-linear  $C_{ds}$

under back-off conditions. Based on a more recent published work [4], the effects of transistor's non-linear output capacitance,  $C_{ds}$  on continuous class-J operation was taken into account to further improve the performance.

# 3.2 Class-BJ/ Continuous Class-J Amplification

The class-J power amplifier assumes a half-rectified current waveform combined with output loading/ terminations at fundamental and second harmonic frequencies to provide a phase shift of  $45^{\circ}$  and  $90^{\circ}$  in the drain-source voltage at these frequencies, respectively. Further work expanded the design space showing a continuum of solutions based on a half-rectified current waveform, and allowing for a more generalized drain-source voltage (3.1), where parameter  $\alpha$  can be varied over the range of -1 to +1. Each solution results in a pair of fundamental and second harmonic terminations as illustrated in Figure 3.1, all providing the same power and efficiency as tuned Class-B operation. This design method adds a level of simplicity in PA design and

Figure 3.2: Average 2-way Doherty efficiency for 6.5, 8, and 10 dB PAPR signals as a function of peaking to carrier power (ideal Doherty operation)

circuit realization, as it gives more freedom in choosing circuit topologies that exhibit the correct loading at fundamental and second harmonic frequencies.

$$v_{ds}(\alpha) = V_{dd}(1 - \cos(\theta))(1 - \alpha\sin\theta)$$

(3.1)

More recently, effects of transistor non-linear output capacitance  $C_{ds}$  on continuous Class-J amplifier performance were analyzed for a Si based LDMOS transistor [4]. It was shown that  $C_{ds}$  non-linearity causes the magnitude of the second harmonic reflection coefficient at the device intrinsic drain terminal ( $\Gamma_{2fo}$ ) to be less than 1 for certain values of  $\alpha$  and greater than 1 for other values, leading to either enhanced or degraded power & efficiency performance as a function of  $\alpha$ . As GaN devices exhibit similar non-linear  $C_{ds}$  characteristics, an analysis for GaN devices under Class-J operation also indicates a power and efficiency dependence with  $\alpha$ .

## 3.3 Doherty Amplifier Design

In this work, we choose a two-way asymmetric DPA architecture so as to maximize efficiency performance at 8 dB OBO when driven by multi-carrier LTE signals.

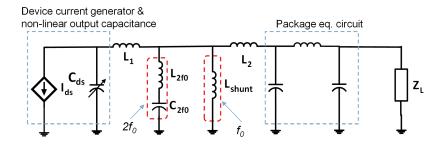

Figure 3.3: Simplified schematic of output matching circuit for Carrier sub-amplifier)

To better understand the trade-offs in choosing DPA asymmetry factor, (i.e., peaking to carrier power ratio,  $P_p/P_c$ ) detailed simulations were performed for amplitude modulated signals to determine average efficiency under the assumption of ideal Doherty characteristics for various values of  $P_p/P_c$ . The results are shown in Figure 3.2 for signal PAPR values of 6.5 dB, 8.0 dB, and 10 dB. At 8 dB OBO, corresponding to 8 dB PAPR, the suggested ratio of  $P_p/P_c \sim 1.5$  is optimal, and a somewhat larger asymmetric ratio is recommended as signal PAPR increases (or equivalently at higher OBO). Therefore, the presented design uses an asymmetry ratio of 1.8, leading to GaN device sizes of about 1.5 mm and 2.7 mm gate width periphery for carrier and peaking devices, respectively.

To further enhance efficiency performance at back-off, the Carrier sub-amplifier is designed for continuous mode Class-J operation, and the effects of non-linear output capacitance  $C_{ds}$  are considered in the design phase, as discussed in Section II. This leads to a circuit solution as illustrated in Figure 3.3, which implements near optimal values for the paired fundamental and second harmonic terminations. The use of a series resonant circuit formed by  $L_{2f0}$  and  $C_{2f0}$  creates a low impedance at the second harmonic frequency, while  $L_1$  and  $C_{ds}$  provide flexibility to position the angle of  $\Gamma_{2f0}$  as required while maintaining the magnitude of  $\Gamma_{2f0}$  close to 1.0. Furthermore, inductor  $L_{shunt}$  provides an additional degree of freedom in setting the value of

Figure 3.4: Illustration of DPA elements in a QFN package

$\Gamma_{f0}$  (fundamental frequency) independent of  $\Gamma_{2f0}$ . For the Peaking sub-amplifier, a simple tuned Class-B output configuration is chosen, since the Peaking sub-amplifier contribution to efficiency at back-off is small in Doherty operation.

An illustration of the DPA elements within the QFN package is given in Figure 3.4. Si-based IPDs are utilized to implement RF impedance pre-matching circuits at the inputs to both Carrier and Peaking GaN devices. The pre-matching circuits make input impedances at the package reference plane amicable for realizing the input matching networks (IMNs) in the printed circuit board (PCB). Use is made of the IPD process to implement both capacitors and inductors on Si die blocks, and use of thick metallization is helpful in reducing insertion losses, especially those associated with spiral inductors. Wirebond interconnections are used between various die blocks and package pins. Similarly, the Class-J output network is realized as a combination of bond-wires and L/C components printed on a separate IPD structure. All of the

Figure 3.5: Full Doherty amplifier including QFN package, and external input coupler and output combiner

Figure 3.6: Measured DPA performance under CW drive-up stimulus, (a) gain and am/pm response, and (b) PAE

circuitry easily fits within the 7mm x 7mm QFN package.

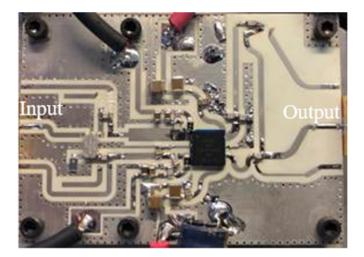

## 3.4 Measured DPA Performance

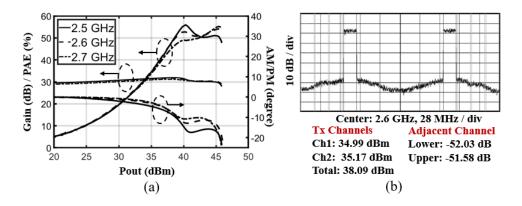

The DPA was implemented in a Rogers R04350 PCB ( $\epsilon_r$ =3.66) substrate with 20 mils thickness, as illustrated in Figure 3.5. The drain (supply) voltage of both carrier and peaking devices were set at 48 V. The carrier amplifier was biased at class-AB with quiescent drain current of 16 mA. The peaking amplifier was biased at class-C with gate voltage of -5.5 V. An uneven-split hybrid coupler from Anaren was used as the input coupler. The DPA was initially characterized with a CW stimulus to obtain AM-AM and AM-PM behavior. The test set up ramped the power level quickly to minimize device heating/thermal affects from significantly influencing the measurement. Drive up data is illustrated in Figure 3.6. Small signal gain is in the range of 11 to 12 dB, and saturated power of approximately +45 dBm. It can be observed that the Peaking amplifier transitions to from an off- to on-state around +37 dBm output power, resulting in some compression of the carrier amplifier and roughly a 1 dB dip in the AM-AM response. The deviation in AM-PM is kept within about 10 degrees, and PAE about 54% is recorded at +37 dBm output power.

| Tab | le | 3.    | 1 |

|-----|----|-------|---|

| 100 | 10 | · • • | - |

| DPA Performance | Under | Multı- | Carrier | LTE Stimulus |

|-----------------|-------|--------|---------|--------------|

|                 |       |        |         |              |

1.1.1.0

| Pout  | LTE Signal BW | PAR  | Efficiency (%) | ACLR-Adj(dBc) |        | ACLR-Alt(dBc) |        |

|-------|---------------|------|----------------|---------------|--------|---------------|--------|

| (dBm) | (MHz)         | (dB) |                |               |        |               |        |

|       |               |      |                | After DPD     |        | After DPD     |        |

|       |               |      |                | L             | U      | L             | U      |

| 37.04 | 1x20          | 7.0  | 48.79          | -54.07        | -53.55 | -56.76        | -55.84 |

| 37.04 | 2x20          | 7.0  | 48.79          | -55.32        | -55.11 | -55.50        | -55.76 |

| 37.01 | 3x20          | 7.5  | 48.68          | -53.20        | -52.23 | -53.46        | -53.05 |

| 37.04 | 5x20          | 7.5  | 48.79          | -50.43        | -50.67 | -50.73        | -50.72 |

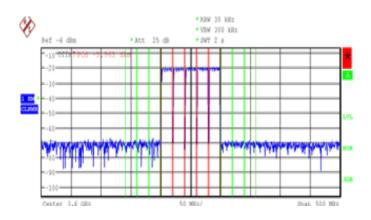

Figure 3.7: Doherty output spectral response under a 5 carrier LTE signal at 20 MHz / carrier, after DPD correction

The DPA performance when driven by multi-carrier LTE signals is tabulated in Table 3.1 for several signal bandwidths and PAPR. Excellent DPD correction is obtained for multi-carrier bandwidth signals of 100 MHz. The excellent DPD linearizability can be attributed in large part to minimizing AM-AM and AM-PM fluctuations over power drive up. Spectral performance at the PA output for a 100 MHz bandwidth LTE signal after DPD correction is shown in Figure 3.7. Excellent DPD amplifier corrected performance is shown across 500 MHz of bandwidth. Table 3.2 summarizes the performance of the proposed DPA with other state-of-the art 3.5 GHz GaN DPA designs. While maintaining a compact form factor, this work demonstrates comparable performance with excellent DPD corrected linearity compared with other DPAs. The presented solution is the only GaN DPA solution that offers the integration of harmonic trapping using a Si-based IPD with carrier and peaking amplifiers housed in a single package, thus enabling a compact solution.

## Table 3.2

| Ref. | Freq. | PAE @ 8dB | PAE   | Tech. | P <sub>sat</sub> | Inst. Band- | ACLR after |

|------|-------|-----------|-------|-------|------------------|-------------|------------|

|      | (GHz) | OBO (%)   | @ Sat |       |                  | width(MHz)  | DPD (dBc)  |

|      |       |           | (%)   |       |                  |             |            |

| [26] | 3.5   | 59*       | 69    | GaN   | 42.9             | 20          | -43        |

| [48] | 3.5   | 55        | 65    | GaN   | 45               | 20          | -52        |

| [27] | 3.5   | 47        | 44    | GaN   | 45               | N/A         | N/A        |

| This | 3.5-  | 54-55     | 64-70 | GaN   | 45               | 20          | -53.55     |

| Work | 3.65  |           |       |       |                  |             |            |

Comparison with Other 3.5 GHz DPAs

\*Estimated from CW plots

# 3.5 Summary

This work describes an approach used to implement a highly efficient GaN-based Class-J Doherty power amplifier in a small footprint. Active GaN devices with their input pre-matching and class-J output circuitry are placed in a 7 mm x 7 mm quad-flat no-leads (QFN) plastic encapsulated package. Under CW excitation, the DPA delivers +45 dBm peak power from 3.5 GHz to 3.65 GHz. At 8 dB OBO, the efficiency reaches 54%, and 70% at peak power. The DPA demonstrates excellent DPD linearized performance of better than 50 dB ACLR with multi-carrier LTE signaling.

## Chapter 4

# 2.6-GHZ INTEGRATED LDMOS DOHERTY POWER AMPLIFIER FOR 5G BASESTATION APPLICATIONS

## 4.1 Introduction

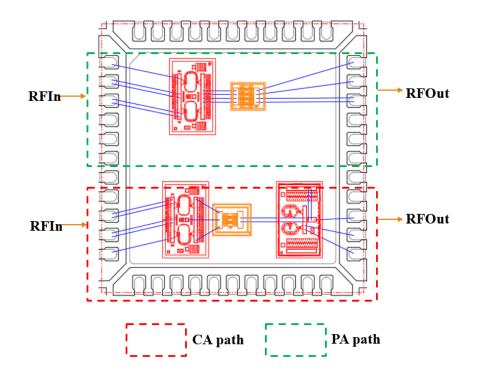

As it was previously discussed in Chapters 1 and 3, DPAs are the most widely used PA architecture in basestation applications because of their simple configuration and high output power back-off (OBO) efficiency [5]-[10]. Traditionally, DPAs have been implemented in discrete fashion with packaged power transistors and distributed matching structures for base stations applications. With the roll-out of 5G, the DPA footprint is becoming more restricted, thus requiring higher levels of DPA integration and miniaturization. Many recently published works have explored fully integrated or partially integrated DPA architectures [11]-[22]. Among them are some promising solutions, such as the integrated Doherty [11]-[14], Doherty PA module [15],[16], and Doherty MMIC [17]-[22].

Traditionally, the DPA output combiner includes quarter-wave transmission-lines (TLs) for proper load modulation. To reduce the size of the output combining network (OCN), these TLs are in-part or entirely replaced by lumped components for miniaturization of Doherty footprints in designs below 6 GHz. *C-L-C* based " $C_{ds}$ -absorption" is one simple and effective method to replace a quarter wave impedance inverter with lumped components for integrated Doherty architectures[11]-[13]. However, to-date, this combining topology has only been implemented in symmetric Doherty [12] and multi-way Doherty [11], [13] PA designs. This combining has not been well-adopted in the two-way asymmetric Doherty architecture because of the asymmetry presented

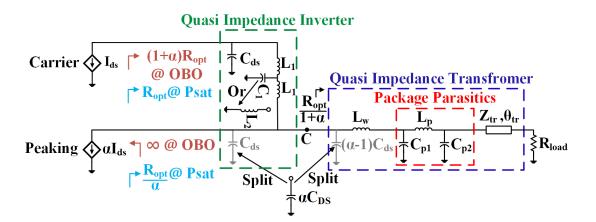

Figure 4.1: Proposed integrated Doherty output combining network (OCN)

by the carrier and the peaking amplifiers'  $C_{ds}$ . Additionally, prior analyses have not provided a generalized case for any two-way DPA architecture and they have not accounted for the effects of bondwire and package parasitic components. In this work, we present for the first time a generalized " $C_{ds}$ -absorption" based Doherty OCN that is applicable for two-way symmetric/asymmetric DPA architectures and considers the effects of bondwire and package parasitic components. The proposed network presents a novel method of absorbing part of the peaking amplifier's  $C_{ds}$  into the impedance transformer network for an asymmetric Doherty, and the OCN offers enhanced flexibility for impedance inverter design. Based on the presented combiner, an asymmetric two-way, two-stage integrated Doherty was designed and fabricated at 2.6 GHz using NXP's AF3 LDMOS process [23]. The experimental results of the fabricated DPA and its performance comparison with other state-of-the-art works are presented in this letter.

# 4.2 Theory of Operation

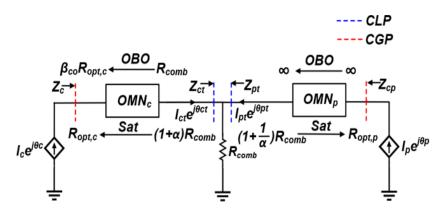

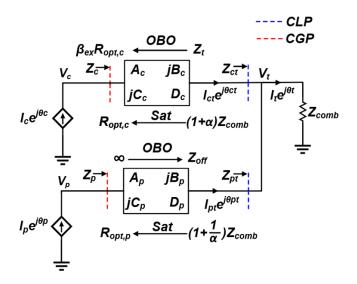

An integrated Doherty with carrier to peaking power ratio of  $1:\alpha$  is selected for the proposed OCN, as shown in Figure 4.1 ( $\alpha=1$  for the symmetric case).

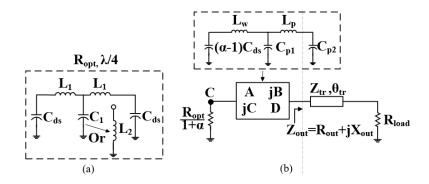

Figure 4.2: (a) Quasi impedance inverter, and (b) Parasitic components of the quasi impedance transformer replaced by ABCD network

Following the parallel equivalence of capacitors from circuit theory, the peaking amplifier's drain-source capacitance,  $\alpha C_{ds}$ , is assumed to be split into  $C_{ds}$  and  $(\alpha - 1)C_{ds}$  across the combining node (C in Figure 4.1). A  $\pi$ -network is formed by  $C_{ds}(\text{carrier})-L_1-(C_1 \text{ or } L_2)-L_1-C_{ds}$  (split from the peaking PA's  $\alpha C_{ds}$ ), and this network comprises the quasi impedance inverter. Bondwire  $(L_w)$  is required to connect the combining node to the package lead. The quasi impedance transformer is composed of  $(\alpha - 1)C_{ds}$ , bondwire  $(L_w)$ , package parasitics  $(C_{p1}-L_p-C_{p2})$ , and a printed circuit board (PCB) microstrip TL  $(Z_{tr}, \theta_{tr})$ . For a symmetric DPA  $(\alpha=1), (\alpha-1)C_{ds}$ does not exist and the peaking PA's  $C_{ds}$  is entirely absorbed by the quasi-inverter.

Load modulation is the key for Doherty operation, as the OCN presents different impedances to the output of the carrier and peaking PAs at OBO and saturated power conditions, as shown in Figure 4.1. For successful load modulation, the quasi-inverter should have a characteristic impedance of  $R_{opt}$  (class-B optimal load resistance) and an electrical length of  $\lambda/4$ , as illustrated in Figure 4.2(a). These two conditions can be satisfied simultaneously when  $L_1$ ,  $C_1$ , and  $L_2$  are calculated from the following:

Figure 4.3: Schematic of proposed two-stage integrated Doherty

$$L_1 = \frac{R_{opt}}{\omega(1+Q_{dev})},\tag{4.1}$$

$$C_1 = \frac{1 - Q_{dev}^2}{\omega R_{opt}}, \qquad \text{if } Q_{dev} \le 1 \qquad (4.2)$$

$$L_2 = \frac{R_{opt}}{\omega(Q_{dev}^2 - 1)}, \qquad \text{if } Q_{dev} \ge 1 \qquad (4.3)$$

Where  $\omega = 2\pi f_0$  is the angular frequency, and  $Q_{dev} = \omega R_{opt}C_{ds}$  is the intrinsic device quality factor.  $R_{opt}$  and  $C_{ds}$  can be extracted from class-B load-line analysis and C-V characteristics to determine  $Q_{dev}$ . If  $Q_{dev}$  approaches unity, then both  $C_1$ and  $L_2$  present open-circuit conditions following (4.2) and (4.3), and the quasi-inverter reduces to  $C_{ds}$ - $2L_1$ - $C_{ds}$ , which is the same solution as the well-known C-L-C inverter. If  $Q_{dev}$  is less than or greater than unity, a shunt capacitor,  $C_1$ , or a shunt inductor,  $L_2$ , is required for an optimum quasi-inverter design. Hence, the proposed quasi-inverter offers additional solutions and more design flexibility when  $Q_{dev}$  is not unity.

A quarter-wave TL of characteristic impedance  $((R_{load}R_{opt})/(1+\alpha))^{1/2}$  can ideally establish a single-section match between the load impedance,  $R_{load}$ , and the combining

#### Table 4.1

| A                                                                                                                           | $1 - \omega^2 (C_{p2}L_p - L_w (C_{p2} + C_{p1}\delta_2))$                    |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|--|--|

| В                                                                                                                           | $\omega(L_p + L_w \delta_1)$                                                  |  |  |  |

| C                                                                                                                           | $(\alpha - 1)\omega C_{ds}\delta_2 + (C_{p2} + C_{p1}\delta_2)\omega\delta_3$ |  |  |  |

| D                                                                                                                           | $(1-\alpha)\omega^2 C_{ds}L_p + \delta_1\delta_3$                             |  |  |  |

| $\delta_1 : 1 - \omega^2 C_{p1} L_p,  \delta_2 : 1 - \omega^2 C_{p2} L_p,  \delta_3 : 1 - (\alpha - 1) \omega^2 C_{ds} L_w$ |                                                                               |  |  |  |

ABCD Parameters for Figure 4.2(b)