## A CMOS Sigma-Delta Digital Intermediate Frequency

to Radio Frequency Transmitter

by

Yongping Han

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved January 2012 by the Graduate Supervisory Committee:

Sayfe Kiaei, Chair Hongyu Yu Bertan Bakkaloglu James Aberle Hugh Barnaby

ARIZONA STATE UNIVERSITY

May 2012

#### **ABSTRACT**

During the last decades the development of the transistor and its continuous down-scaling allowed the appearance of cost effective wireless communication systems. New generation wideband wireless mobile systems demand high linearity, low power consumption and the low cost devices. Traditional RF systems are mainly analog-based circuitry. Contrary to digital circuits, the technology scaling results in reduction on the maximum voltage swing which makes RF design very challenging. Pushing the interface between the digital and analog boundary of the RF systems closer to the antenna becomes an attractive trend for modern RF devices. In order to take full advantages of the deep submicron CMOS technologies and digital signal processing (DSP), there is a strong trend towards the development of digital transmitter where the RF upconversion is part of the digital-to-analog conversion (DAC). This thesis presents a new digital intermediate frequency (IF) to RF transmitter for 2GHz wideband code division multiple access (W-CDMA). The proposed transmitter integrates a 3-level digital IF current-steering cell, an up-conversion mixer with a tuned load and an RF variable gain amplifier (RF VGA) with an embedded finite impulse response (FIR) reconstruction filter in the up-conversion path. A 4th-order 1.5-bit IF bandpass sigma delta modulator (BP  $\Sigma \Delta M$ ) is designed to support in-band SNR while the out-of-band quantization noise due to the noise shaping is suppressed by the embedded reconstruction filter to meet spectrum emission mask and ACPR requirements. The RF VGA provides 50dB power scaling in 10-dB

steps with less than 1dB gain error. The design is fabricated in a 0.18µm CMOS technology with a total core area of 0.8 x 1.6 mm<sup>2</sup>. The IC delivers 0dBm output power at 2GHz and it draws approximately 120mA from a 1.8V DC supply at the maximum output power. The measurement results proved that a digital-intensive digital IF to RF converter architecture can be successfully employed for W-CDMA transmitter application.

#### **ACKNOWLEDGMENTS**

First, I would like to extend my most sincere gratitude and infinite thanks to my main advisor Professor Sayfe Kiaei, I have no words to express the admiration and respect that I have for him. It has been an honor of having been student under his direction. He is an example of researcher, and professional, always conducting himself with the highest values and showing at all times talent, leadership and strict discipline.

I would like to thank my co-advisor Professor Bertan Bakkaloglu for his support during all these years. I thank him for giving me valuable advice about the research. He is a source of inspiration for all of us that have the luck of having worked close to him.

Second, I would like to thank Dr. Tino Copani for his great support and valuable inputs on the research. I also want to thank Dr. Shahin Mehdizad Taleie for his great help on the research topic.

Finally, I would like to express my great gratitude to my parent, sisters, relatives and friends for their continuous encouragement and support.

## TABLE OF CONTENTS

|                                                           | Page   |

|-----------------------------------------------------------|--------|

| LIST OF TABLES                                            | vii    |

| LIST OF FIGURES                                           | viii   |

| CHAPTER                                                   |        |

| 1 INTRODUCTION                                            | 1      |

| 1.1 Motivation and application                            | 1      |

| 1.2 Outline of the thesis                                 | 3      |

| 2 TRANSMITTER ARCHITECTURES                               | 4      |

| 2.1 Overview of transmitter architectures                 | 5      |

| 2.1.1 Super-heterodyne transmitter architecture           | 5      |

| 2.1.2 Homodyne transmitter architecture                   | 9      |

| 2.1.3 Digital heterodyne transmitter architecture         | 11     |

| 2.2 Proposed transmitter architecture                     | 15     |

| 3 SYSTME DESIGN OF THE PROPOSED W-CDMA TRANS              | MITTER |

|                                                           | 21     |

| 3.1 W-CDMA transmitter link budget analysis               | 21     |

| 3.1.1 System linearity requirement                        | 21     |

| 3.1.2 DAC + FIR linearity                                 | 26     |

| 3.2 System design of IF band-pass sigma-delta modulator . | 30     |

| 3.3 System design of band-pass FIR reconstruction filter  | 33     |

| 3.4 Summary                                               | 38     |

| CHAPTER Page                                              |  |

|-----------------------------------------------------------|--|

| 4 DESIGN AND IMPLEMENTATION OF IF TO RF DAC40             |  |

| 4.1 Top-level implementation of IF to RF upconverter 40   |  |

| 4.2 Design of FIR reconstruction filter                   |  |

| 4.3 A 1.5-bit IF DAC input signal generation              |  |

| 4.4 IF switching cell                                     |  |

| 4.5 Gilbert-cell mixer                                    |  |

| 4.6 Frequency divider and clock buffer                    |  |

| 4.7 Summary                                               |  |

| 5 DESIGN OF RF VARIABLE GAIN AMPLIFIER49                  |  |

| 5.1 RF VGA frequency band selection                       |  |

| 5.2 Wide linear dynamic range                             |  |

| 5.3 gm insensitive to temperature variation               |  |

| 5.4 RF VGA circuit implementation                         |  |

| 5.5 RF VGA simulation results and layout                  |  |

| 5.5.1 Input and output LC tank frequency response         |  |

| 5.5.2 Linearity                                           |  |

| 5.5.3 Power steps for different input bit setting at 27°C |  |

| 5.5.4 RF VGA output power variation over temperature      |  |

| 5.5.5 RF VGA chip layout                                  |  |

| 5.6 Summary67                                             |  |

| 6 EXPERIMENTAL RESULTS70                                  |  |

| CHAPTER    |                                                        | Page |

|------------|--------------------------------------------------------|------|

| 7 EXTENTE  | ED APPLICATIONS                                        | 77   |

| 7.1 In     | troduction                                             | 77   |

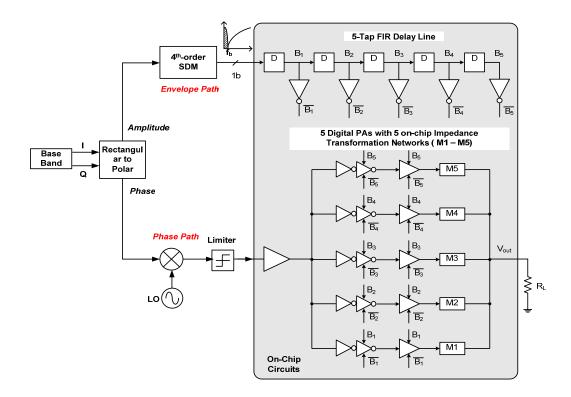

| 7.2 Pr     | oposed digital polar transmitter                       | 79   |

| 7.3 Sy     | ystem design of the proposed digital polar transmitter | 81   |

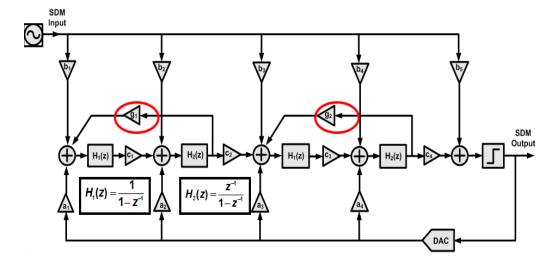

| 7.3.1      | Wideband single-bit sigma-delta modulator              | 81   |

| 7.3.2      | 5-tap FIR reconstruction filter                        | 85   |

| 7.3.3      | Concept of high-efficient on-chip power combining      | 87   |

| 7.4 St     | ımmary                                                 | 91   |

|            |                                                        |      |

| 8 CONCLU   | SIONS                                                  | 93   |

|            |                                                        |      |

| REFERENCES |                                                        | 95   |

# LIST OF TABLES

| Table |                                                               | Page |

|-------|---------------------------------------------------------------|------|

| 1.    | Summary of transmitter architectures                          | 17   |

| 2.    | W-CDMA transmitter specifications                             | 22   |

| 3.    | W-CDMA special emission mask requirement                      | 22   |

| 4.    | Simulated SNR with signal BW of 5MHz with OSR =25             | 33   |

| 5.    | The logic used for DAC                                        | 44   |

| 6.    | RF VGA design specifications                                  | 50   |

| 7.    | RF VGA performance summaries                                  | 68   |

| 8.    | Summary of the measured performances                          | 75   |

| 9.    | Summaries of the specifications and performances of the RFDAC |      |

|       | architectures                                                 | 76   |

# LIST OF FIGURES

| Figure | Page                                                                        |

|--------|-----------------------------------------------------------------------------|

| 1.     | Traditional super-heterodyne transmitter architecture                       |

| 2.     | Variable IF transmitter architectures 8                                     |

| 3.     | Conventional homodyne transmitter architecture                              |

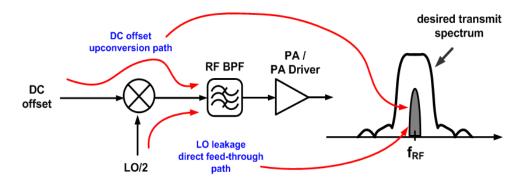

| 4.     | Homodyne transmitter architecture issue                                     |

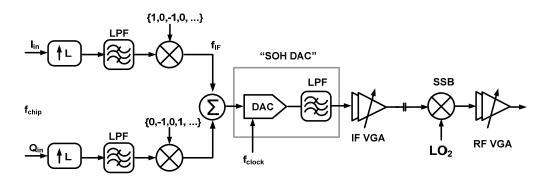

| 5.     | Digital heterodyne transmitter architecture proposed in [10]                |

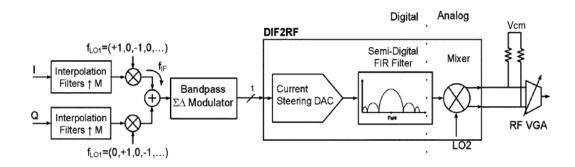

| 6.     | Digital IF to RFDAC transmitter architecture proposed in [11] 12            |

| 7.     | Proposed CMOS digital IF transmitter                                        |

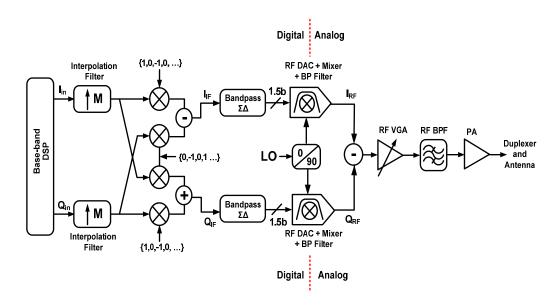

| 8.     | W-CDMA IF spectrum after 40-tap BP FIR filtering                            |

| 9.     | The RFDAC+Mixer+BP filter block of the proposed RFDAC                       |

|        | modualtor                                                                   |

| 10.    | Non-linear transmitter analysis setup                                       |

| 11.    | Plot of transmitter OIP3 vs. ACPR at 5MHz offset                            |

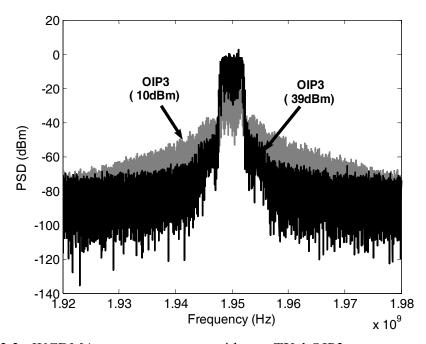

| 12.    | W-CDMA output spectrums with two sets of transmitter OIP3 25                |

| 13.    | Simplified RFDAC circuit                                                    |

| 14.    | RFDAC IMD3 vs. normalized current source resistance                         |

| 15.    | The relationship between in-band SNR and out-of-band noise 31               |

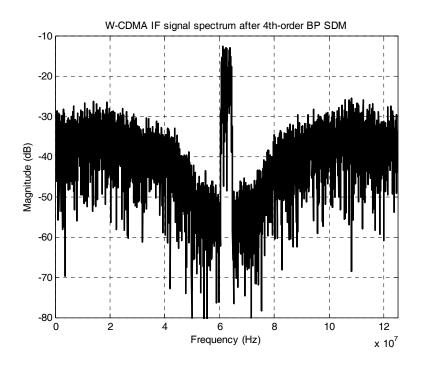

| 16.    | W-CDMA IF signal after 4 <sup>th</sup> . –order BP sigma-delta modulator 33 |

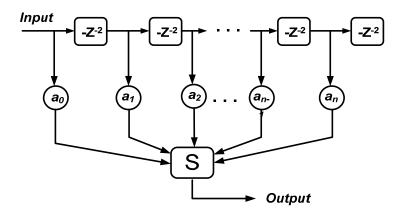

| 17.    | Band-pass FIR filter structure                                              |

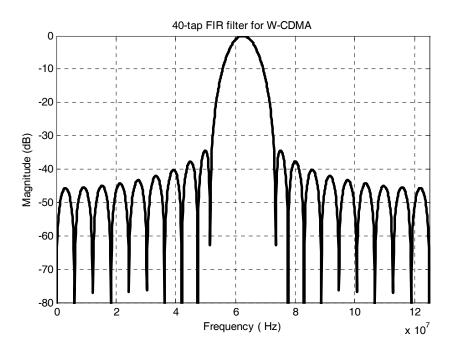

| 18.    | 40-tap band-pass FIR magnitude response for W-CDMA                          |

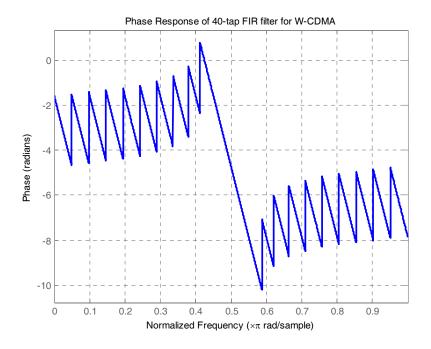

| 19.    | 40-tap band-pass FIR phase response for W-CDMA                              |

| 20.    | 40-tap FIR filter magnitude response for 2.4GHz WLAN band 37                |

| Figure |                                                                | Page   |

|--------|----------------------------------------------------------------|--------|

| 21.    | 40-tap FIR filter phase response for 2.4GHz WLAN band          | 37     |

| 22.    | 40-tap FIR filter magnitude response for both W-CDMA and W     | LAN    |

|        | 802.11g bands                                                  | 38     |

| 23.    | Top-level schematic of digital IF to RF converter with BP      |        |

|        | reconstruction filter                                          | 41     |

| 24.    | The DC current source array forming the FIR filter response (W | -      |

|        | CDMA or WLAN)                                                  | 43     |

| 25.    | 1.5-bit DAC signal generation                                  | 44     |

| 26.    | The IF switch cell for N <sub>th</sub> tap                     | 45     |

| 27.    | The Gilbert-cell based RF upconversion mixer                   | 46     |

| 28.    | Frequency divider with division ratio of 8                     | 47     |

| 29.    | VGA design strategy                                            | 52     |

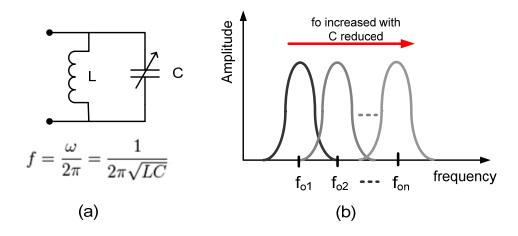

| 30.    | (a) Tunable LC tank (b) Frequency response of tunable LC tank  | k . 55 |

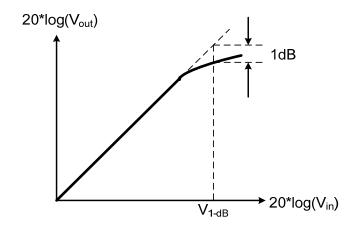

| 31.    | Graphic interpretation of a linear system                      | 56     |

| 32.    | 1-dB compression point                                         | 56     |

| 33.    | Resistor degeneration with the cross-coupled current bleeding  |        |

|        | technique                                                      | 57     |

| 34.    | Resistor degeneration                                          | 58     |

| 35.    | Constant-gm biasing circuit for RF VGA                         | 60     |

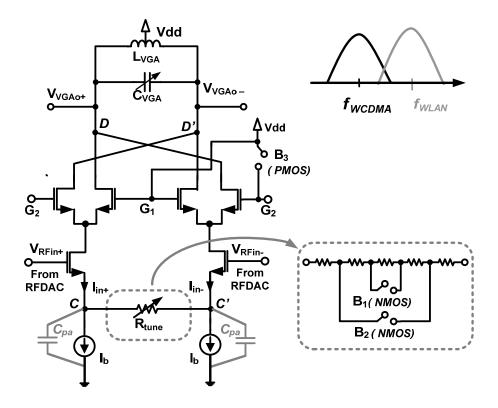

| 36.    | Schematic diagram of the proposed VGA                          | 62     |

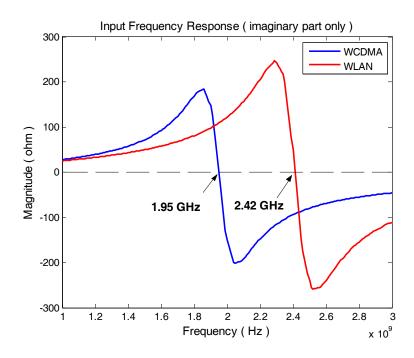

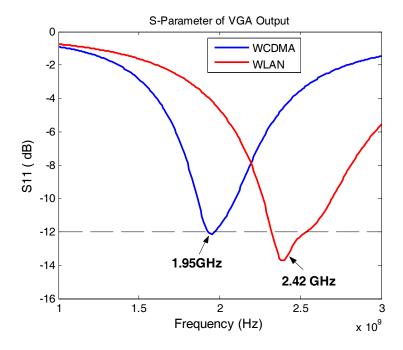

| 37.    | RF VGA input frequency response (imaginary part only)          | 64     |

| 38.    | RF VGA output return loss based on 50ohm load matching         | 64     |

| Figure |                                                                       | Page  |

|--------|-----------------------------------------------------------------------|-------|

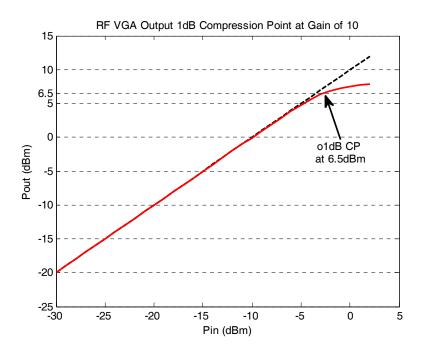

| 39.    | OIP1dB of RF VGA for W-CDMA                                           | 65    |

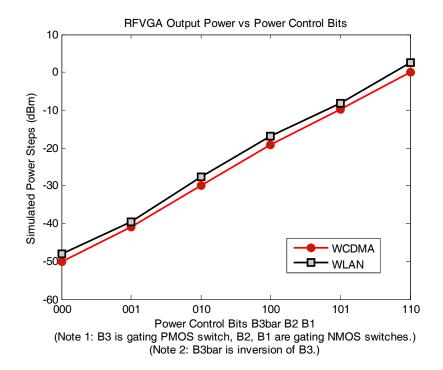

| 40.    | Power steps vs. different bits                                        | 66    |

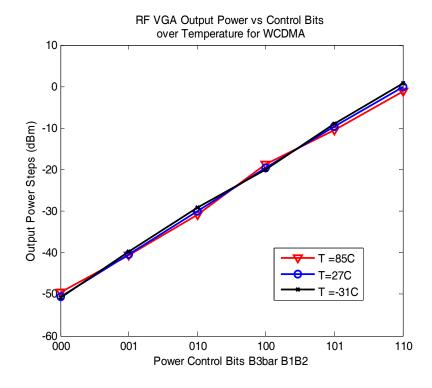

| 41.    | Power steps vs. control bits at -31°C, 27°C, 85°C (W-CDMA)            | 66    |

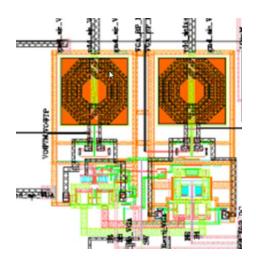

| 42.    | Layout of designed RF VGA                                             | 67    |

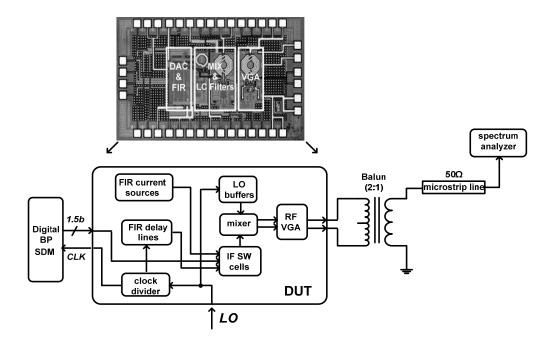

| 43.    | Measurement setup for the proposed design                             | 71    |

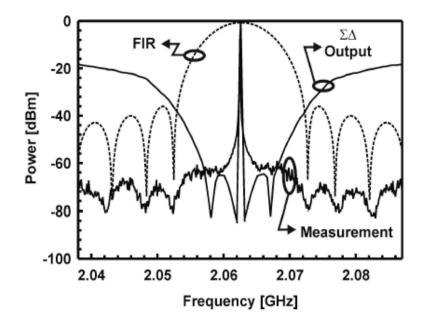

| 44.    | Ideal BP FIR response, BP $\sum \Delta$ modulated signal and measured |       |

|        | single-tone spectrum                                                  | 71    |

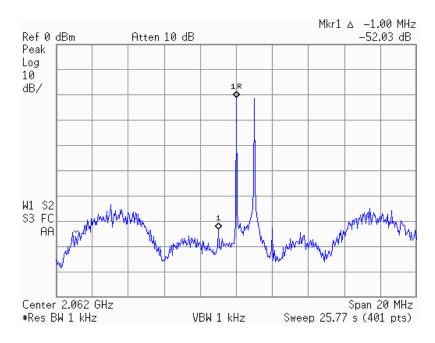

| 45.    | Measured IMD3 performance based on the two-tone test                  | 72    |

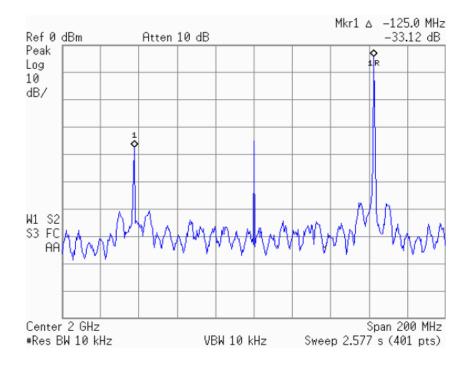

| 46.    | Measured image rejection result                                       | 72    |

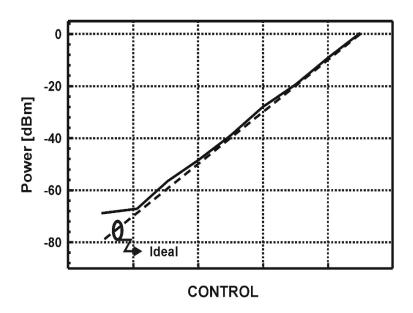

| 47.    | Measured power variation for the proposed transmitter (CONTR          | OL is |

|        | from the DSP in the transmitter)                                      | 74    |

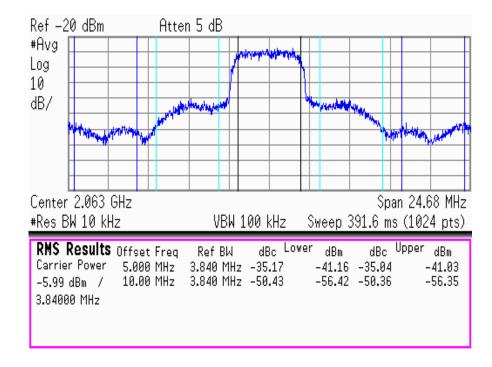

| 48.    | Measured W-CDMA ACPR performances                                     | 74    |

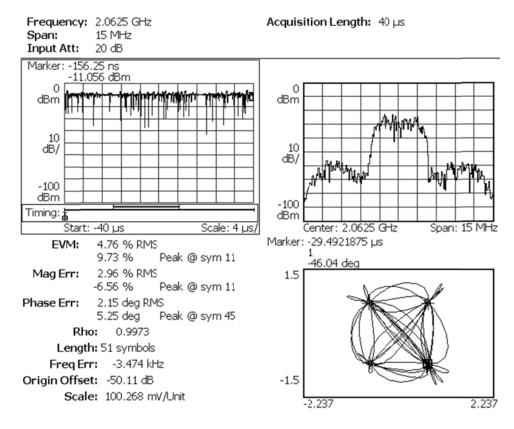

| 49.    | Measured W-CDMA rms EVM performance                                   | 75    |

| 50.    | Proposed digital polar transmitter architecture                       | 80    |

| 51.    | 1-bit 4 <sup>th</sup> order low pass sigma-delta modulator with OSR=5 | 83    |

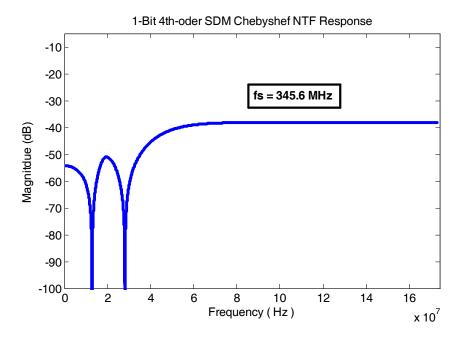

| 52.    | 1-bit 4 <sup>th</sup> . –order SDM Chebyshelf NTF response            | 84    |

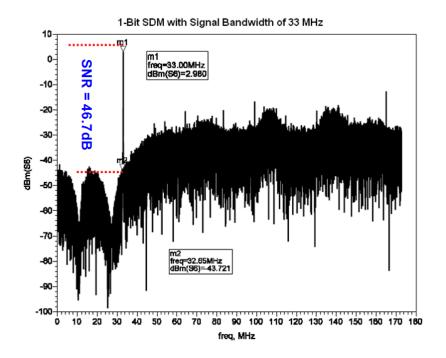

| 53.    | 1-bit wide-band sigma-delta modulator frequency response              | 84    |

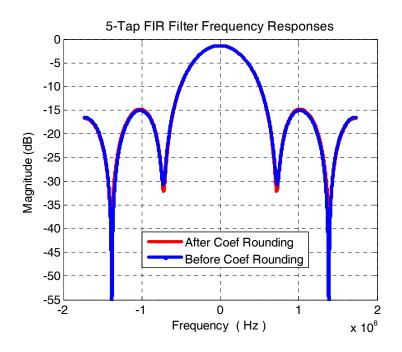

| 54.    | 5-tap FIR filter frequency response                                   | 86    |

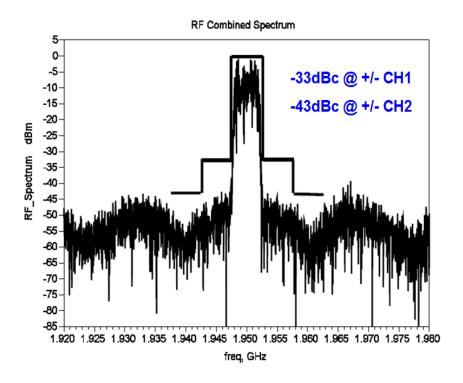

| 55.    | 5-tap FIR filtered W-CDMA RF spectrum                                 | 86    |

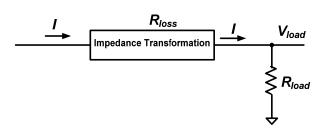

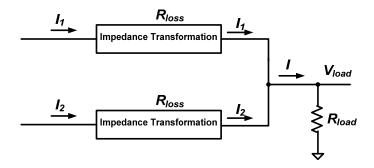

| 56.    | One-section lossy impedance transformation network                    | 87    |

| 57.    | Two-section lossy impedance transformation network                    | 88    |

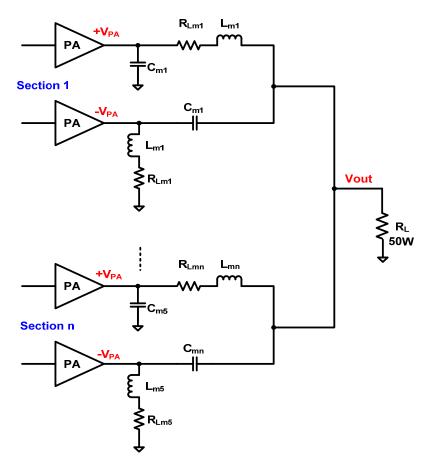

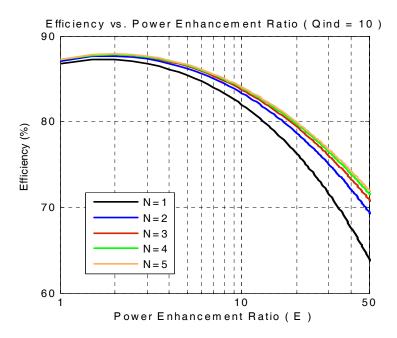

| 58.    | Lossy on-chip multi-section FIR power combining                       | 89    |

| Figure |                                                               | Page |

|--------|---------------------------------------------------------------|------|

| 59     | Power efficiency of the impedance transformation network as a |      |

|        | function power enhancement ratio with different sections      | 91   |

#### CHAPTER 1

### **INTRODUCTION**

### 1.1 Motivation and application

With the increasing demand for high linearity, power efficient and wide-bandwidth mobile devices, RF systems will benefit from moving the interface between the digital to analog domains closer to the antenna. Furthermore, in order to take advantages of the deep submicron CMOS technologies and digital signal processing (DSP), there is a strong trend towards the development of digital heterodyne architectures where the digital baseband signal is up-converted to intermediate frequency (IF) in the digital region, and RF up-conversion is part of the digital-to-analog conversion (DAC).

The digital to RF up-conversion methods included current- steering DAC cells [2-4], multi-bit  $\Sigma\Delta$  noise shaped IF [2], and the inherently linear single-bit RFDACs [3]. The digital heterodyne transmitter has the advantages of higher integration level and power efficiency, improved I/Q matching and EVM performance, and adaptive modulation of the transmitted signal bandwidth without the need of external IF SAW filter [1]. In addition, the problems associated with conventional homodyne transmitters including DC-offset and LO leakage, are greatly reduced because there is no analog gain stage in the baseband. The RF DAC presented in [2] shows better signal-to-noise ratio (SNR), lower power consumption and reduced hardware complexity compared to the conventional DAC-Mixer architecture. In this architecture, higher SNR is achieved by using multi-bit (8-level)  $\Sigma\Delta M$  with high sampling frequency of

514MHz. However, the multi-bit DAC could require additional mismatch reduction techniques, such as dynamic element matching, which could increase the system complexity and power consumption. The architecture of RFDAC presented in [3] offers advantages in terms of high integration due to digitalintensive design and higher linearity. The impact of flicker noise up-conversion due to the DAC's current sources is reduced by alternating the operation point of the rail device from accumulation to inversion. Also jitter masking technique is employed to minimize IF jitter impact, which ensures that the current source is off during the DAC bit switching transition. However, the design shows some limitations, which make it hard to be used in the wideband transmitter applications. One limitation is inadequate filtering of the out-of-band quantization noise. In most wireless standards high adjacent channel power suppression and strict spectral emission requirements are enforced. In order to meet the spectrum emission mask and ACPR requirements, a more complex FIR filter is required to suppress the out-of-band quantization noise. Another limitation is the use of single-ended local oscillator (LO) that drives the gate of the rail device, which leads to higher LO leakage compared to that of the conventional Gilbert-cell mixer.

This objective of this work is to research a digital IF to RF transmitter (DRFTx) architecture which can be utilized in the wide-band transmitter applications with high linearity, circuit simplicity and low power consumption. The DRFTx architecture presented in this thesis is a digital heterodyne transmitter which utilizing a 3-level digital IF to RF DAC up-converter, followed by a RF

variable gain amplifier with an embedded band-pass reconstruction filter to take the advantages of RFDAC [3] while overcome its limitations so that the idea of RFDAC presented in [3] can be successfully extended to the real world W-CDMA transmitter application.

### 1.2 Outline of the thesis

This thesis consists of eight chapters with the introduction as the first one. Chapter 2 presents the surveys of the transmitter architectures including the conventional super-heterodyne, homodyne, and the recent digital heterodyne architecture, followed by the proposed the digital IF transmitter architecture. Chapter 3 analyzes the system requirements of the proposed architecture which provides the baseline requirements on the design of the reconstruction FIR filter, RFDAC and RF VGA. Chapter 4 shows the circuit level implementation of the major building blocks of the proposed architecture including RFDAC with embedded FIR reconstruction filter and Chapter 5 demonstrates the design of discrete-power-step RF VGA. Chapter 6 illustrates the measurement results which demonstrate that the proposed architecture is feasible for W-CDMA transmitter application. Chapter 7 presents the potential extended applications, and the conclusions are drawn in Chapter 8.

#### CHAPTER 2

### TRANSMITTER ARCHITECTURES

The objective a radio transmitter is to up-convert the baseband signal and amplify it to the desired power level before delivering it to the transmit antenna. For a transmitter that is designed for wide-band mobile or wireless communication systems, especially for W-CDMA transmitter, high dynamic range, high linearity, low power consumption and low cost are the most important properties. W-CDMA class III mobile transmitters are targeted for a maximum power of +24dBm and a minimum of -50dBm at the antenna end which leads to a minimum of 74dB dynamic range requirement. In the W-CDMA standard, the transmitter linearity requirement can be transferred to the W-CDMA transmit waveform quality which is specified by the Adjacent Channel Leakage Ratio (ACLR) or Adjacent Channel Power Ratio (ACPR) and the RMS Error Vector Magnitude (EVM). For W-CDMA systems, ACLR is defined as the ratio of the integrated signal power in the adjacent channel to the integrated signal power in the main channel; the standard demands minimum 33dBc and 43dBc at the first channel (5MHz) and the second channel (10MHz) offset respectively [5]. EVM is a measure of how much the deviation of the transmitted constellation construction to the ideal one which is generated at the base band. W-CDMA transmitter specifies RMS EVM to be less than 17.5% at all output power levels greater than 20dBm [5]. The low power consumption property is very crucial for maximizing the battery life time which is an important factor for mobile devices. The low product cost is the most important figure from the end customers point of view,

which is determined by the technology, the integration level and the number of the external components needed to guarantee the transmit waveform quality.

To gain better insight of in the different tradeoffs, first the existing transmitter architectures will be overviewed and discussed, including superheterodyne and homodyne transmitter architectures. Next, the digital heterodyne transmitter will be highlighted. Finally, the digital-intensive digital intermediate frequency (IF) to RF digital-to-analog (DAC) transmitter topology targeted for W-CDMA application is proposed.

#### 2.1 Overview of transmitter architectures

The choice of transmitter architecture has a significant impact on the operation of the system. In general, there are two types of common transmitter architectures: super-heterodyne and homodyne (zero-IF or direct conversion). Each of these architectures has its own inherent advantages and disadvantages. However, many of the potential issues of the individual architecture can be solved with smart topology and / or circuit design techniques.

### 2.1.1 Super-heterodyne transmitter architecture

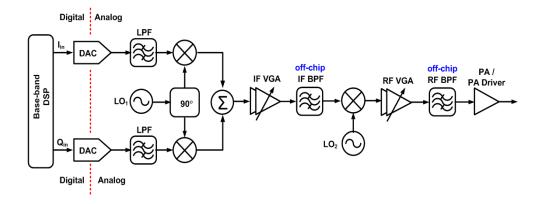

For W-CDMA transmitters, super-heterodyne architecture has been around for many decades, and still the most common architecture reported today [6]–[11]. Figure 2.1 demonstrates the traditional super-heterodyne transmitter architecture.

Figure 2.1: Traditional super-heterodyne transmitter architecture

In the baseband, the in-phase and quadrature-phase (I/Q) digital bit streams are converted to the analog signals through the baseband digital-to-analog converter (DAC). After proper low-pass filtering to reject any high frequency aliasing generated during the digital-to-analog conversion process, the signals are mixed with the first local oscillator (LO) signal and up-converted to intermediate frequency (IF) and combined to generate single-sideband IF signal. Typically the combined IF signal will experience some gain variation stage and the band-pass filtering stage to reduce spurs and further reject any aliasing residues from the DAC, and then mix with the 2<sup>nd.</sup> LO and up-converted to the radio frequency through RF mixer. Finally, the up-converted signal is sent to the RF variable gain amplifier (VGA) followed by RF band-pass filtering and then delivered to the power amplifier (PA) or PA driver. Since the base-band signal is up-converted to the radio frequency in two steps, the super-heterodyne architecture offers many advantages. First of all, the 74dB power control demanded by W-CDMA standard can easily be distributed to the IF VGA and RF VGA stages to relax the limited substrate isolation impact on the achievable transmit dynamic range. Moreover, the waveform quality is superior mainly due to the following two reasons: 1) The LO leakage is a minor issue because the LO<sub>1</sub> and LO<sub>2</sub> are far from the transmit band, and their leakages can be suppressed at the IF BPF and RF BPF stages; 2) The quadrature modulation is performed in the intermediate frequency stages which are relative low frequencies. Therefore the transmit coupling between the in-phase and quadrature-phase paths can be minimized, and the superior matching between I/Q paths can be achieved, leading to almost ideal RMS EVM performance.

However, the good quality waveform offered by the super-heterodyne architecture does come with some high prices. First, it requires an external IF bandpass filter [6]–[9] and an external RF bandpass filter [12] to reject the unwanted spurs and the sidebands, thus driving the overall chip cost, size and power consumption up. Second, since it utilizes two-step up-conversion, two sets of synthesizes are required, leading to a complicated, area and power inefficient designs. In general, the super-heterodyne transmitter architecture is a bulky, power-hungry and high cost approach.

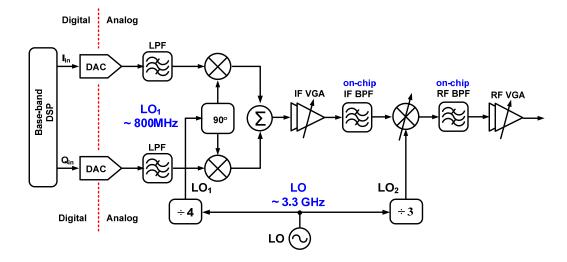

Recently, there are some works called variable-IF heterodyne architectures [10] [11] with the main efforts to eliminate the bulky and expensive IF BPF and insist one synthesizer as shown in Figure 2.2. Figure 2.2(a) implements the variable IF transmitter using on-chip IF and RF BPFs, while Figure 2.2(b) demonstrates alternative variable IF transmitter approach by adopting on-chip complex-IF filters. Note that none of the variable IF transmitters require an off-

chip IF band- pass filter and only one synthesizer is utilized to generate main LO

(a): Variable IF transmitter architecture with on-chip IF and RF BPF

(b): Variable IF transmitter architecture with on-chip complex-IF BPF

Figure 2.2: Variable IF transmitter architectures

signal. The IF and RF LOs are just the divided-down versions of the main LO.

Therefore, the variable IF architecture offers advantages in terms of lower power

consumption and lower cost compared to the traditional super-heterodyne architecture. For the W-CDMA transmit application, since the up-conversion is still implemented in two steps (IF and RF stages), the wide power variation requirement is not an issue for the variable-IF approach. However, the variable IF arheitectures shown in Figure 2.2 are more sensitive to I/Q mismatches compared to the traditional super-heterodyne architecture because the quadrature modulations are now implemented either at high IF frequency (~ 800M) or at RF (2GHz).

## 2.1.2 Homodyne transmit architecture

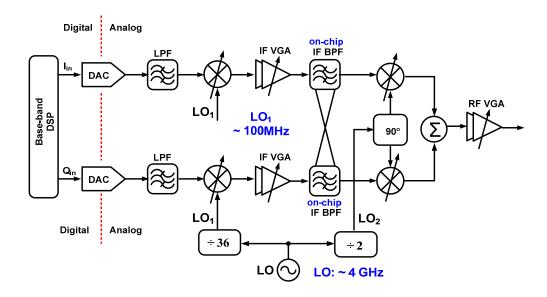

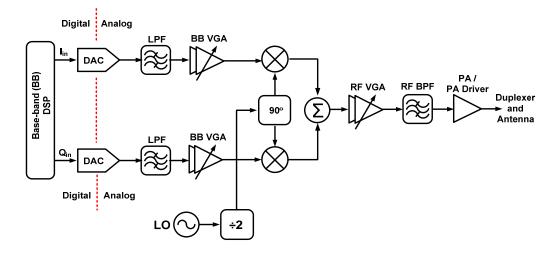

Apart from the two-step up-conversion transmitters described above, homodyne transmitter architectures draw a lot of attenuation these days. Figure 2.3 demonstrates a conventional homodyne transmitter. In this architecture, the baseband digital I and Q bit streams are converted to the analog signals through the baseband DACs. After baseband low-pass aliasing filtering, the filtered signals mix with the only LO and up-converted to the radio frequency, and then the RF I and Q signals are merged and drive PA or PA driver through RF variable gain amplifier and RF band-pass filter.

As shown in Figure 2.3, the homodyne transmitter up-converts the baseband signal to radio frequency in a single step, therefore it completely eliminates the IF band-pass filter and IF synthesizer. As such it offers high integration level, low power consumption and low cost compared to the heterodyne counterpart.

One big issue associated with the traditional homodyne transmitter is that

LO is operating at the exact same frequency as the PA where the strong PA output could couple to the LO and result in the degraded output waveform. This issue is known as LO pulling. One remedy is to offset LO frequency from the operating frequency of the PA as shown in Figure 2.3. By this way, the LO frequency will never overlap the desired transmit band and the LO-pulling issue can be resolved with the cost of increased power consumption due to the higher LO frequency generation.

Figure 2.3: Conventional homodyne transmitter architecture

Even though the LO pulling can be removed from the problem list, another issue is hard to be solved. For W-CDMA transmitter application, the 74dB power variation is hard to implement solely at the RF stage due to the limited substrate isolation, thus the baseband variable gain amplification stage is inevitable. Since there is no ac-coupling in the baseband paths, the dc-offset due to the base-band gain variation stays in the up-conversion path and will sit in the transmit band and degrade the output waveform as shown in Figure 2.4.

Moreover, the LO/2 (LO divided down by 2) leakage signal will directly feed through to the output due to the finite substrate isolation and other non-ideality factors, and ultimately degrade the quality of the output waveform as well [13]. In addition, in the homodyne architecture, since the quadrature modulation is implemented at radio frequency, I/Q mismatches are expected to be higher compared to the heterodyne architecture.

Figure 2.4: Homodyne transmitter architecture issue

## 2.1.3 Digital heterodyne transmitter architecture

As mentioned before, the homodyne architecture shows the advantage of the circuit simplicity, however, it is not a desired approach to transmit W-CDMA signal due to the performance issues associated with the dc-offset and the LO leakage. Super-heterodyne architectures offer performance benefits in terms of high linearity, high dynamic range and superior waveform, but they consume more power consumption, require more off-chip filters and more chip area which shortens the battery life time and drives the devices cost high, therefore it is not an attractive approach either.

Some recent works propose heterodyne transmitters using digital IF

modulator to remove the IF band-pass filter from the transmitter and keep only one synthesizer in the up-conversion path as shown in Figure 2.5 and Figure 2.6. In these transmitter systems, the first up-conversion is implemented the digital domain, hence the digital heterodyne transmitter.

In Figure 2.5, the base-band digital data (running at the chip rate of 3.84MHz) are first upsampled and interpolated, filtered by the following low-pass filter, multiplied with the first quadrature LOs, and then the IF in-phase and quadrature signals are summed together to generate the single-ended IF signal before reaching the DAC. In general, implementing digital modulator requires numerical oscillators (for example, direct digital synthesizer) and multipliers,

Figure 2.5: Digital heterodyne transmitter architecture proposed in [1]

Figure 2.6: Digital IF to RF DAC transmitter architecture proposed in [14]

which could be complicated and power hungry. However, the work in [10] chooses the IF frequency ( $f_{IF}$ ) to be a quarter of the DAC clock update rate ( $f_{clk}$ ), thus the IF LO signals become a bit stream sequence representing values of +1, 0, or -1. Therefore, the IF digital modulation is just a simple sign-bit-flipping logic, which considerably eases the circuit complexity and reduces the power consumption.

Since the quadrature up-conversion is implemented completely in the digital domain, the perfect matching between the in-phase and quadrature-phase paths can be obtained, hence the superior EVM performance. The transmitter shown in Figure 2.6 also adopts the similar idea of digital IF modulation, therefore the excellent waveform quality can be expected as well.

The differences between the two transmitters in Figure 2.5 and Figure 2.6 are mainly demonstrated in the second up-conversion phase. Multi-bit DAC followed by a higher-order low-pass filtering method is implemented in Figure 2.5, while the single-bit DAC with embedded semi-digital reconstruction bandpass filtering topology is employed in Figure 2.6. As shown in Figure 2.5, the single-ended digital IF signal is sent to the 8-bit DAC with the clock update rate of 253.44MHz to guarantee the in-band signal-to-noise ratio (SNR), and the second-order-hold DAC attenuates the spurs and rejects the clock images to meet the W-CDMA spurious emission requirements. Since there are two variable amplifiers both in the IF and RF stages, the 74dB dynamic range demanded by the W-CDMA transmitter can easily be achieved, while the dc offset due to IF gain variation can be removed by the ac-coupling capacitor before the second up-

conversion. However, the multi-bit DAC usually requires additional matching schemes, such as dynamic element matching, to maintain good linearity. Moreover, the aggressive attenuation offered by the second-order-hold DAC could distort the in-band signal, thus the digital correction is needed to recover the transmitting waveform. The additional matching scheme and the digital correction increase the system complexity and drive the ultimate chip area and power consumption up. Different from the multi-DAC approach in [1], the digital transmitter in [14] utilize the single-bit DAC to take advantage of its inherent linearity, no matching for DAC linearity is required. A single-bit 4<sup>th</sup>-order bandpass sigma-delta modulator (BP SDM) is used to generate 1-bit IF bit streams with high in-band SNR, while the out-of-band quantization noise due to the noiseshaping is suppressed by the embedded linear-phase finite impulse filter (FIR) in the second up-conversion. Thanks to the single-bit digital-to-analog conversion, the digital IF to analog RF conversion and the following reconstruction filtering are successfully merged into a single circuit block, leading to a more compact and digital-intensive transmitter design as shown in Figure 2.6. However, the transmitter in [14] shows some drawbacks which are hard for wide-band transmitter applications. One limitation is the inadequate filtering of the out-ofband quantization noise. In order to meet the spectrum emission mask and ACPR requirements, a more complex FIR filter is required to suppress the out-of-band quantization noise. Another limitation is the use of single-ended local oscillator (LO) that drives the gate of the rail device, which leads to higher LO leakage compared to that of the conventional Gilbert-cell mixer.

In general, the digital heterodyne transmitter exhibits the circuit simplicity of the homodyne architecture while inherits the superior performance of the super-heterodyne architecture with proper design.

So far, the three transmitter architectures have been overviewed and discussed. Their circuit characteristics, advantages and disadvantages are summarized in Table 2.1

## 2.2 Proposed digital transmitter architecture

As shown in Table 2.1, the digital heterodyne transmitter surpasses the traditional super-heterodyne and homodyne transmitters in terms of circuit simplicity and good performances. Therefore, it is more suitable for the future generation of wide-band mobile transmit terminals where size, cost and power consumption are the key factors. With the fast development on the CMOS technology, there is a strong trend to push more circuits used to be implemented in the analog region to the digital domain to take advantage of the CMOS technology scaling and the fast-and-flexible digital signal processing (DSP), thus the digital heterodyne transmitter in [14] excels the transmitter in [1] in terms of more intense digital implementation in transmit path and the low-cost CMOS technology used. However, the work in [14] shows some limitations which have already been addressed. In order to extend the idea presented in [14] to the wideband transmitter applications, a modified digital IF to RFDAC transmitter needs to be developed.

Figure 2.7 demonstrates the proposed digital transmitter architecture

implemented in CMOS technology. It consists of 1.5-bit band-pass  $\Sigma\Delta$  Modulator, a wideband digital IF to RF up-conversion DAC followed by a RF VGA with a reconstruction filter embedded in the up-conversion stage. The architecture performs RF up-conversion, mixing the LO signal with 3-level digital IF bit streams, while the quantization noise is suppressed by the semi-digital FIR filter. In the proposed architecture, the digital IF signal is noise-shaped via a 4<sup>th</sup>-order 1.5-bit BP  $\Sigma\Delta$ M to improve in-band SNR, while the out-of-band quantization noise due to noise-shaping is suppressed by the semi-digital FIR filter and analog image reject filter. In this work, the out-of-band quantization noise suppression is designed to meet W-CDMA spectrum emission mask and ACPR requirements [5]. 74dB dynamic range demanded by the W-CDMA standard [5] is distributed to  $\Sigma\Delta$ M stage and RF VGA to overcome substrate isolation limitation.

At the baseband I/Q signals generated from the base-band DSP block are first interpolated and up-sampled from 3.84MHz (W-CDMA chip rate is 3.84Mcps) to  $f_s$ =253.44MHz, and then digitally up-converted to the intermediate frequency (IF) at  $f_{IF}$ = $f_s$ /4= 63.36MHz. By choosing a sampling frequency  $f_s$  within the range from250MHz to 260MHz, digital images will be out of the W-CDMA transmitter and receiver bands [1], thereby relaxing the requirements on the reconstruction filter after the DAC. The digital band-pass IF signal is 1.5-bit noise-shaped via the 4<sup>th</sup>-order band-pass (BP)  $\Sigma\Delta$  Modulator. The 3-level IF signaling reduces the transient glitch and the quantization noise level compared to a 2-level DAC and still maintains good linearity. Also the in-band SNR can be improved by approximately 5dB due to the additional half bit with the same

Table 2.1: Summary of transmitter architectures

| Architecture          | No. of up-<br>conversion | No. of<br>synthesizers/<br>off-chip IF<br>filter | Pros                                                                          | Cons                                       |

|-----------------------|--------------------------|--------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------|

| Super-<br>heterodyne  | 2                        | 2 / 1                                            | High linearity High DR Wide bandwidth Good EVM ACPR                           | Bulky<br>High<br>power<br>High cost        |

| Homodyne              | 1                        | 1 /0                                             | Simple Low power Low cost                                                     | DC offset<br>LO leakage<br>Degraded<br>EVM |

| Digital<br>heterodyne | 2                        | 1 /0                                             | High linearity High DR Wide bandwidth Good EVM ACPR Digital intense Low power |                                            |

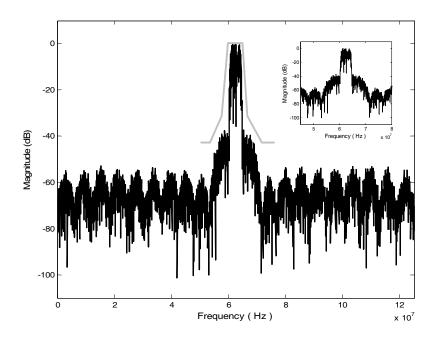

oversampling ratio and the loop-filter order [15]. Moreover, the lower quantization noise level could result in a lower order of the reconstruction filter. From the system level simulations, 1.5-bit  $4^{th}$ -order BP  $\Sigma\Delta M$  is enough to provide in-band SNR with the sampling frequency of 253.44 MHz and the 40-tap BP FIR filter is sufficient to attenuate the out-of-band quantization noise and meet the W-CDMA spectrum emission mask and ACPR requirements. Higher order FIR filter could provide more out-of-band noise suppression, however it leads to higher quiescent power consumption. Figure 2.8 shows the W-CDMA IF spectrum after

Figure 2.7: Proposed CMOS digital-IF transmitter

Figure 2.8: WCDMA IF spectrum after 40-tap BP FIR filtering ( $f_s$ =250 MHz)

the 40-tap FIR filtering. The zoom-in spectrum is shown on the upper-right corner of the figure. The gray line shows the W-CDMA mask.

One big advantage of the proposed architecture is that the traditional transmitter image issue is resolved by maintaining the signals in quadrature format from the baseband to the radio frequency. The accuracy of the single-sideband modulated signal is mainly determined by the first up-conversion quadrature mixers which are implemented in the digital domain in the proposed architecture.

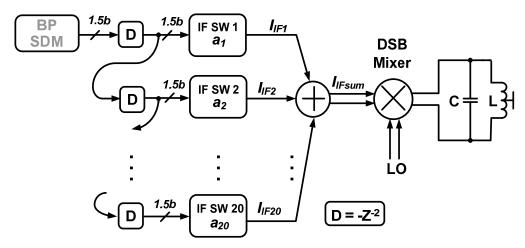

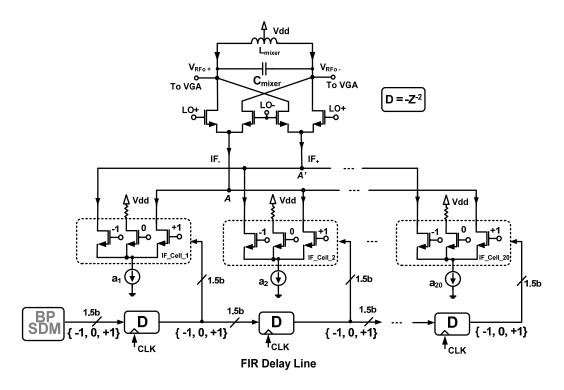

The major building block of RFDAC+Mixer+BP filter of the proposed architecture is illustrated in Figure 2.9. The 1.5-bit noise-shaped digital IF signal generated by the BP  $\Sigma\Delta M$  feeds to the 40-tap FIR delay line, and the FIR delayed 3-level IF signals drive individual IF switch cell. The FIR coefficients ( $a_1$  to  $a_{20}$ ) due to the 40-tap BP FIR filtering are embedded in the IF switching stages and modulate the IF tail currents. The current-mode DAC outputs are summed, mixed with the LO and up-converted to radio frequency through the RF double-sideband (DSB) mixer. The mixer is loaded with an LC band-pass filter.

Figure 2.9: The RFDAC+Mixer+BP Filter block of the proposed RFDAC modulator

The entire block provides four functionalities: digital-to-analog conversion, frequency up-conversion, FIR reconstruction filtering, and the analog out-of-band image rejection filtering.

By adopting the proposed DRFTx architecture, the digital IF to RF converter can be extended for W-CDMA transmitter application with the benefits of circuit simplicity, high linearity and low power consumption.

#### CHAPTER 3

### SYSTEM DESIGN OF THE PROPOSED TRANSMITTER

The design of the proposed W-CDMA transmitter is not straight-forward. First, the linearity requirement of the individual block including RFDAC and RFVGA needs to be derived based on the system level link budget analysis to avoid design randomness. Second, the IF band-pass sigma-delta modulator has to provide enough in-band signal-to-noise (SNR) while keeping the loop filter order as low as possible to ease circuit complexity and reduce power consumption. Finally, the out-of-band quantization noise generated at the BP SDM stage must be suppressed by the reconstruction filter down to the level where the adjacent channel signals are not affected. In this chapter, the system design of the proposed architecture will be presented including the transmitter linearity analysis, IF band-pass sigma-delta modulation and the FIR reconstruction filtering.

## 3.1 W-CDMA transmitter link budget analysis

### 3.1.1 System linearity requirement

In this section linearity and noise analysis of the proposed architecture based on W-CDMA transmitter link budget analysis is derived. The RFDAC non-ideality due to the finite output impedance is analyzed in order to give the lowest boundary for sizing FIR current sources.

Table 3.1 lists the major specifications of W-CDMA transmitter (class III). Table 3.2 lists the W-CDMA spectral emission mask requirements [5].

W-CDMA is a full duplex system where the transmitter and receiver

Table 3.1 W-CDMA transmitter specifications

| Frequency band          | 1920MHz – 1980MHz     |

|-------------------------|-----------------------|

| Channel spacing         | 5MHz                  |

| Chip rate               | 3.84 Mbps             |

| Modulation              | QPSK                  |

| Max. Power at antenna   | 24dBm (+1dB/-3dB)     |

| Max. Power at PA output | 28dBm **              |

| RMS EVM                 | < 17.5%               |

| ACPR                    | -33dBc @ 5MHz offset  |

|                         | -43dBc @ 10MHz offset |

Table 3.2 W-CDMA spectral emission mask requirement [5]

| Δf in MHz      | Relative Requirement in dBc | Measurement BW |

|----------------|-----------------------------|----------------|

| 2.5 - 3.5      | -35 -15*(Δf/MHz -2.5)       | 30kHz          |

| 2.5 - 7.5      | -35 -1*(Δf/MHz -3.5)        | 1MHz           |

| 7.5 - 8.5      | -39 -10*(Δf/MHz -7.5)       | 1MHz           |

| 8.5 – 12.5 MHz | -49                         | 1MHz           |

operate simultaneously at different frequencies. The nonlinear distortion generated by a mobile transmitter can spill over into the adjacent channel, or the receive band and impact received signal bit error rate (BER). Therefore digital cellular standards restrict the amount of emissions permitted in the adjacent and alternate channels. Usually, adjacent channel power arises from the spectral regrowth due to inter-modulation distortions (IMDs) from the transmitter.

In general, the ACPR at the first channel offset is dominated by the 3<sup>rd</sup>order inter-modulation distortion (IMD3), while the ACPR at the second channel

offset is mainly determined by the 5<sup>th</sup>-order inter-modulation distortion (IMD5).

For the W-CDMA transmit signal which occupies a bandwidth of 5MHz, a multitone test [16] [17] is required to predict accurate distortion in the adjacent and

alternate channels which is not an easy task in the transmitter system analysis due

to long and complicated simulations required. Based on the narrow-band

approximation and with a periodic modulating waveform assumption, the

modulated W-CDMA signal issue can be treated as a conventional two-tone test

[18]. With this approach, ACPR requirements can be translated to conventional

IMD3 or OIP3 specifications.

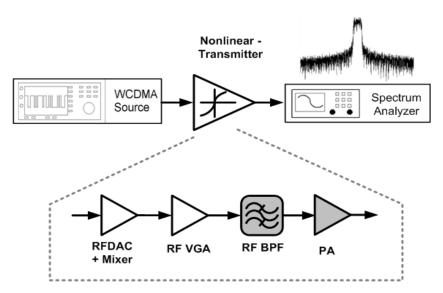

The proposed transmitter can be modeled as a non-linear block in the transmitter analysis using the setup as shown in Figure 3.1. In this setup, an ideal W-CDMA baseband signal drives the non-linear transmitter and ACPR

Figure 3.1: Non-linear transmitter analysis setup

performances are evaluated at the output using a spectrum analyzer. The nonlinear transmitter includes RFDAC with mixer, RF VGA, RF BPF and PA in cascade. The relationship between ACPR at the first channel offset and OIP<sub>3</sub> of the transmitter including PA can be approximately expressed based on the two-tone test as follows:

$$ACPR_{TX} \cong 2(P_{TX} - OIP_{3,TX}) - 9 + C_0 + 10\log_{10}\left(\frac{BW_{ACP}}{BW}\right)$$

(3.1)

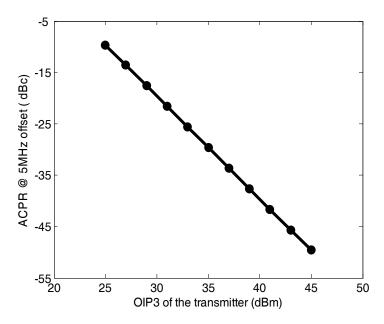

where  $C_0 \cong 0.85 * (PAR - 3)$ , PAR is the peak-to-average ratio of the transmitted signal which is 3.28dB for  $\pi/4$ -QPSK modulated signal.  $ACPR_{TX}$ ,  $P_{TX}$ ,  $OIP_{3,TX}$  are the ACPR performance, the transmitted power and OIP3 at the transmitter output respectively.  $BW_{ACP}$  represents the measuring bandwidth for the adjacent channel power which is 3.84MHz for W-CDMA signal, and BW is the desired transmitted signal bandwidth after taking the roll-off factor of 0.22 into account [19]. According to the standard, the ACPR at 5MHz and 10MHz offsets from the center of the main channel must be less than -33dBc and -43dBc, respectively [5]. Figure 3.2 shows the ACPR and OIP<sub>3</sub> of the transmitter based on the equation (1) with the transmitted power of 25dBm which is targeted to the W-CDMA band I class III power level (when taking additional 2dB loss due to duplexer at the antenna end). From the Fig. 3.2, to achieve better than -33dBc ACPR at 5MHz offset, the minimum transmitter OIP<sub>3</sub> is required to be at least +36.7dBm. In the proposed design, OIP3 of 38dBm at the PA output is chosen as a design target to leave 3 to 4dB margin for ACPR at first channel offset. Fig. 3.3 shows the output of the spectrum with different OIP3s which emphasizes how the linearity of the

transmitter impact on the ACPR performances.

Figure 3.2: Plot of transmitter OIP3 vs. ACPR at 5MHz offset

Figure 3.3: WCDMA output spectrums with two TXs' OIP3s

#### 3.1.2. DAC +FIR linearity

In the proposed architecture, the transmitter linearity in terms of OIP3 or IMD3 is determined by the RFDAC, the VGA, RF BPF and the PA. The overall transmit linearity specification can be expressed by equation (3.2) [19]. Since the linearity of the RF BPF is usually close to ideal, the equation (3.2) can be simplified as equation (3.3). From equation (3.3), in order to relax linearity requirements on the RFVGA and PA, the FIR DAC and mixer linearity must be optimized.

$$\frac{1}{OIP3_{TX}} = \frac{\frac{1}{G_{VGA} * G_{BPF} * G_{PA}}}{OIP3_{REDAC}} + \frac{\frac{1}{G_{BPF} * G_{PA}}}{OIP3_{VGA}} + \frac{\frac{1}{G_{PA}}}{OIP3_{RFF}} + \frac{1}{OIP3_{PA}}$$

(3.2)

$$\frac{1}{OIP3_{TX}} = \frac{\frac{1}{G_{VGA} * G_{BPF} * G_{PA}}}{OIP3_{RFDAC}} + \frac{\frac{1}{G_{BPF} * G_{PA}}}{OIP3_{VGA}} + \frac{1}{OIP3_{PA}}$$

(3.3)

where  $OIP3_{TX}$ ,  $OIP3_{RFDAC}$ ,  $OIP3_{VGA}$ ,  $OIP3_{PA}$  are the output  $3^{rd}$  order intercept points of the transmitter, RFDAC and mixer, RF VGA and PA, respectively.  $G_{VGA}$  and  $G_{PA}$  are the power gains of the RF VGA and PA.  $G_{BPF}$  is the loss of the RF BPF.

Using a commercial PA MAX2291 [11] (ACPR of -38dBc at the first channel offset with  $P_{out} = 28$ dBm which translates into  $OIP3_{PA} = 42.2$ dBm,  $G_{PA} = 27$ dB) and with the designed RF VGA targeted for OIP3 of +16dBm and the maximum power gain of 10dB, the OIP3 of the RFDAC and mixer should be at +14.3dBm from equation (3.3) with 2dB loss due to RF BPF.

The major source of nonlinearity of current steering DACs is the finite

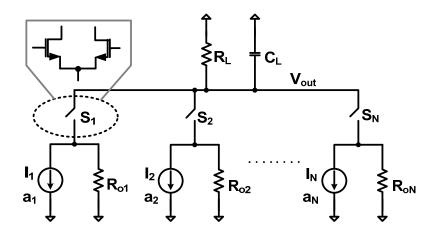

output impedance of DAC current sources [21]. In order to better understand how the output impedances of FIR based DACs impact on the linearity of the transmitter, the up-conversion switching quad is considered ideally linear. Therefore, nonlinear behavior of the RFDAC is analyzed using the simplified model of Figure 3.4, where  $a_1$  to  $a_N$  are the coefficients of the FIR filter.  $I_1$  to  $I_N$  are the FIR-scaled current sources with finite output impedances  $R_{o1}$  and  $R_{oN}$ . Moreover,  $S_1$  to  $S_N$  are the IF switches and  $R_L$  is the equivalent mixer's output load resistance at the resonance frequency of 2GHz which is set by the LC tank in Figure 3.4. Since the mixer is ideal, the nonlinearity from the FIR DAC will directly appear at the mixer output, and mixer switches are neglected in the simplified circuit.

Figure 3.4: Simplified RFDAC circuit

Defining  $I_0$  as the normalized current and  $g_0$  as the normalized conductance related to  $I_0$ , we have

$$a_1 = I_1/I_0 = 1, \ a_1 = I_2/I_0, \ \dots, \ a_N = I_N/I_0$$

(3.4)

$$g_{o1} = 1/R_{o1}, \ g_{o2} = 1/R_{o2}, ..., g_{oN} = 1/R_{oN}; \ g_L = 1/R_L$$

(3.5)

where  $a_1, a_2, ..., a_N$  are the FIR coefficients.  $g_{o1}, g_{o2}, ..., g_{oN}$  are the conductances of the current sources  $I_1$  to  $I_N$ , respectively.

For a sinusoidal output  $V_{out}$  each of the DAC switches is either ON or OFF at a given time [20].

$$s(t)_{on} = \frac{1 + \sin \omega t}{2} , \quad s(t)_{off} = \frac{1 - \sin \omega t}{2}$$

(3.6)

The total output conductance when the N switches are "on" is

$$g_{out,on} = g_L + ((a_1 + a_2 + \dots + a_N) \cdot g_0 \cdot s(t)_{on})$$

$$= g_L + \sum_{i=1}^{N} a_i \cdot g_0 \cdot \left(\frac{1 + \sin \omega t}{2}\right)$$

(3.7)

and the total complementary output conductance is

$$g_{out,off} = g_L + \left( \left( a_1 + a_2 + \dots + a_N \right) \cdot g_0 \cdot \left( \frac{1 - \sin \omega t}{2} \right) \right)$$

(3.8)

The differential output voltage is

$$V_{out,diff} = \frac{4 \cdot g_L \cdot F_N \cdot I_0 \cdot \sin \omega t}{4g_L^2 + 4g_L \cdot g_0 \cdot F_N + F_N^2 \cdot g_0^2 \cdot (1 - \sin^2 \omega t)}$$

(3.9)

where  $F_N = \sum_{i=1}^{N} a_i$  is the sum of the normalized FIR coefficients.

Assigning  $x = \sin \omega t$  (a single-tone excitation)

yields

$$V_{out,diff} = \frac{4 \cdot g_L \cdot F_N \cdot I_0 \cdot x}{4g_L^2 + 4g_L \cdot g_0 \cdot F_N + F_N^2 \cdot g_0^2 \cdot (1 - x^2)}$$

$$= \frac{H \cdot x}{1 + O \cdot (1 - x^2)} \tag{3.10}$$

where

$$H = \frac{4 \cdot g_L \cdot F_N \cdot I_o}{4g_L^2 + 4g_L \cdot g_o \cdot F_N}$$

$$Q = \frac{F_N^2 \cdot g_o^2}{4g_L^2 + 4g_L \cdot g_o \cdot F_N}$$

Using Taylor expansion,

$$V_{out,diff} = A_1 \cdot x + A_3 \cdot x^3 \tag{3.11}$$

Since the fundamental tone and the third-order components have the following relationship [12]

$$IMD3 = \frac{4}{3} \cdot \left| \frac{A_1}{A_3} \right| = \frac{\frac{14}{3} F_N^2 \cdot g_0^2 + \frac{16}{3} \left( g_L^2 + g_L \cdot g_0 \cdot F_N \right)}{F_N^2 \cdot g_0^2}$$

(3.12)

The OIP3 of the FIR DAC is

$$OIP3_{RFDAC} = G_{RFDAC} + \frac{IMD3_{RFDAC}}{2} + P_{IN,RFDAC} = \frac{IMD3}{2} + P_{OUT,RFDAC}$$

(3.13)

where  $G_{FIRDAC}$  is the gain of the FIR DAC in dB,  $P_{IN,RFDAC}$  and  $P_{OUT,RFDAC}$  are the input and output power of the RFDAC. Since the OIP3 of RFDAC is at least 14.3dBm, and the  $P_{OUT,RFDAC}$  is designed to be maximum of -10dBm, the minimum  $IMD_3$  of RFDAC is set to be about 49dB based on equation (3.13).

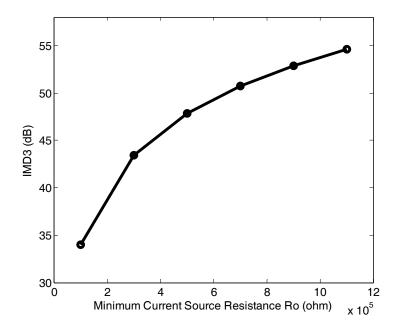

Figure 3.5 shows the impact of the finite output impedances of 40-tap FIR current sources on the IMD3 of the RFDAC. In order to achieve -38dBc ACPR at 5MHz offset, IMD3 of the RFDAC needs to be at least 49dB, which translates to the minimum unit current source output impedance of  $600k\Omega$ .

Figure 3.5: RFDAC IMD3 vs. normalized current source resistance

#### 3.2 System design of IF band-pass sigma-delta modulator

The design of 1.5-bit IF band-pass sigma-delta modulator is mainly targeted for the high in-band SNR while keeping the loop-filter order as low as possible. In order to ease the design of the following DAC and eliminate extra matching circuitries, 1.5-bit quantizer is chosen. Compared to the inherent linear 1-bit DAC, 3-level DAC reduces the transient glitch and the quantization noise level and still maintains good linearity. Also the in-band SNR can be improved by approximately 5dB due to the additional half bit with the same oversampling ratio and the loop-filter order [21]. Moreover, the lower quantization noise level could result in lower order of the reconstruction filter.

From the wave quality requirement of W-CDMA, in-band SNR needs to be at 36dB (equivalent to 6-bit ENOB). With the quantizer bit is fixed at 1.5-bit

level, the order of the filter needs to be derived to provide minimum 36dB in-band SNR. For the sigma-delta modulator with the same quantizer bit, the higher the order the higher the SNR can be achieved based on the following equation [22]:

$$SNR_{P} = \frac{3\pi}{2} (2B - 1)^{2} * (2n + 1) * (\frac{OSR}{\pi})^{2n + 1}$$

(3.14)

where the  $SNR_P$  is the full-scale SNR, B is the quantizer bit, n is the loop-filter order, OSR is the over-sampling ratio.

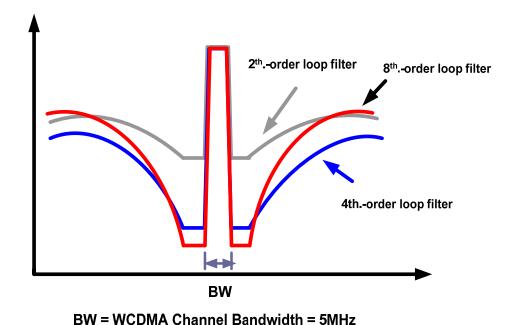

However as shown in Figure 3.6, the higher loop-filter order results in higher out-of-band quantization noise level due to the more aggressive noise-shaping. In order to suppress the out-of-band noise below the required ACPR levels, the higher order reconstruction filter order is required and will ultimately

Figure 3.6: The relationship between the in-band SNR and out-of-band noise with different loop-filter orders (same quantizer bits)

complicate the design and drive the circuit power consumption high. On the other hand, if the filter order is low, even though the out-of-band quantization noise level is low compared to the higher-order ones, it might not provide enough in-band SNR and degrade the ultimate W-CDMA wave quality. Therefore there is trade-off among in-band SNR, the sigma-delta loop filter order and the following reconstruction filter order.

For the current design, the IF is fixed at 62.5MHz with the digital LO frequency at 250MHz due to the image issue explained before. Therefore, the sampling frequency fs is equal to 250MHz, and the signal bandwidth  $f_{BW}$  is equal to 5MHz, the OSR is about 25 using the following equation [15]:

$$OSR = \frac{f \sqrt{2}}{f_{BW}} \tag{3.15}$$

Up to now, the minimum SNR, the quantizer bit and OSR are given, the order of the loop filter can be derived from the simulations using different loop-filter order. Table 3.3 lists the simulated SNR with OSR =25 and the signal BW of 5MHz. From the table, 2<sup>nd</sup>.-order loop filter can only provide marginal in-band SNR, when taking the degradation happening along the following upconversion path, approximately 38dB in-band SNR is absolutely not enough. From the simulation results, a 4<sup>th</sup>.-order bandpass sigma-delta modulator is chosen based on the decent in-band SNR it offers. Figure 3.7 shows the W-CDMA IF signal after the 1.5-bit 4<sup>th</sup>-order band-pass sigma-delta modulator.

Figure 3.7: W-CDMA IF signal after 4<sup>th</sup>.-order BP sigma-delta modulator

Table 3.3: Simulated SNR with signal BW of 5MHz with OSR = 25

| Loop filter order              | Quantizer bits | SNR (dB) |

|--------------------------------|----------------|----------|

| 2 <sup>nd</sup> . – order (BP) | 1.5            | ~ 38     |

| 4 <sup>th</sup> – order (BP)   | 1.5            | ~ 62     |

# 3.3 System design of band-pass FIR reconstruction filter

W-CDMA transmitter demands minimum 33dBc and 43dBc ACPR at the first channel (5MHz) and the second channel (10MHz) offset, while the 3-level IF signals contain high out-of-band quantization noise due to the noise-shaping from the IF band-pass sigma-delta modulator. Without proper filtering the out-of-band noise, it is impossible for the proposed transmitter to meet the ACPR

requirements.

The main purpose of the using FIR filter as reconstruction filter is its linear-phase property which is critical to maintain linearity of the transmit signal after filtering. Moreover, the FIR coefficients can be easily programmed to fit different transmit standards, therefore, it has the potential for the reconfigurable multi-band transmitter applications.

The general structure of band-pass FIR filters is illustrated in Figure 3.8, and the equation representing the structure can be expressed as [23]

$$H_{FIR}(z) = a_0 + a_1 * (-z^{-2}) + \dots + a_{n-1} * (-z^{-2})^{n-1} + a_n * (-z^{-2})^n$$

(3.16)

where the  $a_0$ ,  $a_1$ ,  $a_2$ , ...,  $a_{n-1}$ , and  $a_n$  are the FIR coefficients, and  $-z^{-2}$  is the bandpass delay unit, and n is the filter order. From equation (3.16), the filter frequency response is determined by the FIR coefficients and the filter orders.

Figure 3.8: Band-pass FIR filter structure

In order to meet the W-CDMA ACPR requirement while keeping low the filter order, different types of windows are examined, including Rectangular, Kaiser, Triangler and Hann. With the multiple iterations, a 36-tap FIR filter using

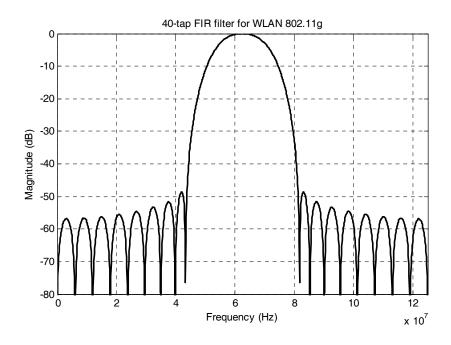

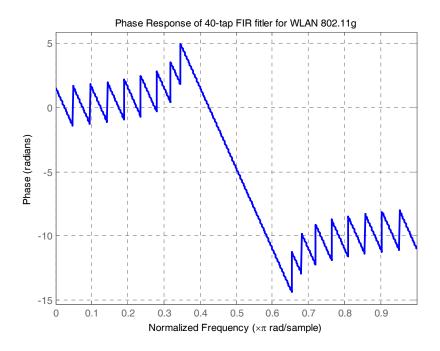

Kaiser window and Beta equal to 3 is found to meet the W-CDMA emission mask requirements for the clock rate of 250MHz. For real circuit implementation, the exact coefficients are hard to achieve. Therefore, the rounded FIR coefficients are used. Taking the FIR coefficient rounding effect and the real silicon non-ideality into account, 40-tap FIR filter is more realistic to meet the target. Figure 3.9 shows the 40-tap band-pass FIR filter frequency response without rounding, and its phase frequency response is shown in Figure 3.10.

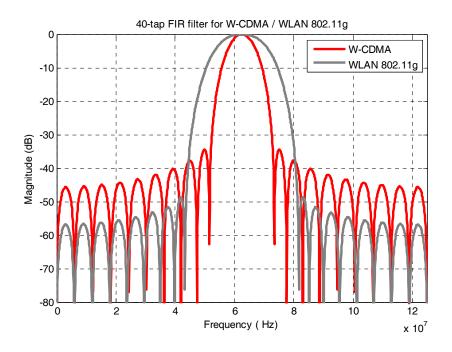

As mentioned before, one reason to pick the FIR filter for the signal reconstruction is its programmability. With the same FIR filter order and different FIR coefficients, the filter can be used as the reconstruction filter for other transmit band, for instance, the 2.4GHz WLAN 802.11g band. Figure 3.11 plots the 40-tap FIR frequency response for 2GHz WLAN transmit band, and its phase frequency response is shown in Figure 3.12. Figure 3.13 shows the magnitude frequency response for both W-CDMA and WLAN 802.11g on the same plot to have better view of 40-tap FIR filter for both transmit bands in terms of bandwidth, notches and out-of-band roll-off.

Figure 3.9: 40-tap band-pass FIR magnitude response for W-CDMA

Figure 3.10: 40-tap band-pass FIR phase response for W-CDMA

Figure 3.11: 40-tap FIR filter magnitude response for 2.4GHz WLAN band

Figure 3.12: 40-tap FIR filter phase response for 2.4GHz WLAN band

Figure 3.13: 40-tap FIR filter magnitude responses for both W-CDMA and WLAN 802.11g bands

# 3.4 Summary

In the chapter the linearity requirements of each individual blocks including RFDAC and RFVGA have been derived based on the system link budget analysis and will be used as the guideline for the circuit implementations. From the linearity analysis in order to meet target ACPR of -38dBc at the first channel offset, OIP3 of RFV GA needs to be at least +14.3dBm at the maximum gain of 10 and the minimum unit current source resistance has to be greater than  $600k\Omega$ . A 1.5-bit 4<sup>th</sup>-order band-pass sigma-delta modulator has given based on the trade-off in terms of in-band SNR, out-of-band quantization noise level and the reconstruction filter order. The FIR reconstruction filter has been designed to

meet W-CDMA transmitter emission requirements. Also the programmability of the FIR filter has been demonstrated using 2.4 GHz WLAN 802.11g band as an example.

#### CHAPTER 4

#### DESIGN AND IMPLEMENTATION OF IF TO RF DAC

The proposed digital IF to RFDAC transmitter has been integrated in a four-metal 0.18µm CMOS technology. The chip includes major circuits of digital IF to RF converter with embedded band-pass reconstruction FIR filter, RF VGA, clock buffers and frequency dividers. In this chapter, the design and implementation of the FIR reconstruction filter and RFDAC core are presented. The critical design specifications are given based on the W-CMDA transmitter system analysis in chapter 3. Since the RF VGA is a standalone block, the design of RF VGA will be demonstrated in the chapter 5 separately.

## 4.1 Top-level implementation of IF to RF upconversion

Fig.4.1 shows the top level schematic of digital IF to RF converter with embedded BP FIR filter. It includes a current-steering DAC, 1.5-bit digital IF switching cells, FIR filter and Gilbert-cell up-converter. Since 40-tap BP FIR filter is adopted for this design, there are 20 delay cells each of which realizes inverse of two unit delays based on  $-z^{-2}$  in the digital domain, hence 20 IF switching cells each of which is driven by the delayed 3-level digital noise-shaped IF signal. The 20 non-zero FIR coefficients  $a_1$  to  $a_{20}$  are embedded in the current sources of the IF switching stages. The output currents from all IF switching stages are summed and sent to the LO quad and then up-converted to the desired frequency of 2GHz. By absorbing FIR coefficients into the current sources of IF switching stages, the RFDAC, up-conversion mixer and BP FIR filter are merged

Figure 4.1: Top-level schematic of digital IF to RF converter with BP reconstruction filter

into a compact block.

The three-level IF signaling is achieved in the DAC path by adding a current dump path to the two-level DAC. Therefore there is a positive path corresponding to +1, a negative path corresponding to -1, and a dump path related to 0. As shown in Fig. 4.1for each current source there is an IF switch cell which consists of three NMOS devices to implement the 3-level DAC signaling. Each tap from 1 to 20 has a different DC current weighted by the FIR filter coefficients, therefore the DC current in the conducting device of the IF switches will be different for each tap. For the circuit level implementation of the FIR filter coefficients, DC current sources are used. The DC current sources are implemented using NMOS transistors, and sizes of the transistors are scaled by

the filter coefficients. The length of the current source devices is chosen such that they can achieve the desired output impedance. The output impedances of the current sources should be greater than the value derived in Chapter 3. The widths of NMOS devices consist of multiples of a unit device size for good matching between current sources and the multiples are actually the scaled filter coefficients. The device sizes are symmetrical around the center to maximize phase linearity, so there are only 10 different filter coefficients. The gate voltage of the NMOS devices is biased through a constant-gm current bias circuit. The design and implementation trade-offs of each individual sub-blocks including FIR reconstruction filter, 3-level DAC input signal generation, IF switch cell and RF mixer will be covered from section 4.2 to 4.5.

### 4.2 Design of FIR reconstruction filter

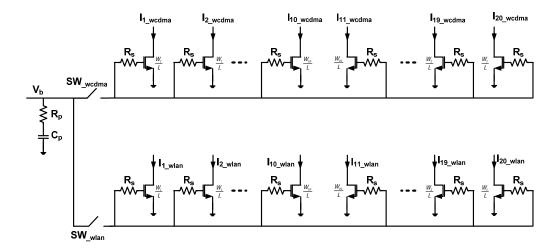

There are two sets of current source arrays as shown in Figure 4.2. Depending on the standard of operation (W-CDMA or WLAN) one set is turned ON or the other. The selection circuit connects or disconnects the gate of the NMOS current sources to a bias voltage or to ground.

The FIR filter coefficients are implemented by the DC current sources as shown in Figure 4.2, which applies for both sets of current sources. The widths

W1 to W10 are different for two modes. The NMOS transistors with Length=0.72um (3 times the minimum length of the process) are used in order to get high output resistance current sources which directly affects the linearity. The widths of NMOS devices consist of multiples of a unit device size for good

Figure 4.2 The DC current sources forming the FIR filter response (W-CDMA or WLAN)

matching between current sources and the multiples are actually the filter coefficients. The device sizes are symmetrical around the center (W1=W20, I1=I20). The gate voltage of the NMOS devices is biased through a constant-gm current bias circuit "Vb" as shown in Figure 4.2. The bias voltage is grounded by Cp which is about 4pF to filter noise that is coupled to the bias circuitry. In order to avoid oscillation which may occur in bond-wire inductors of the DC ground and the Cp and also the parasitic capacitors, a damping resistor Rp=10  $\Omega$  is added in series to the CP and a high resistor Rs=3.6K $\Omega$  is added in series to the gate bias.

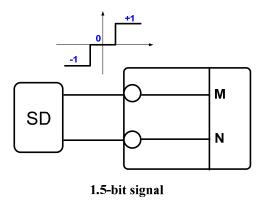

# 4.3 A 1.5-bit IF DAC input signal generation

The DAC operates as 1.5-bit DAC (3-level DAC). There are two inputs to the DAC, M and N as shown in Fig.4.3. A three level quantizer is used in noise

shaping and two inputs are taken from the  $\Sigma\Delta$  modulator, M and N as shown in Figure 4.3. The addition of the third level is achieved quite simply by adding a dump path to the existing two-level DAC and some simple digital decoding. The DC currents of each unit current source of the current steering DAC have three paths, positive, negative and a dump path. Since the FIR filter is a bandpass filter with factor 2 of interpolation, there is going to be  $Z^{-1}$  and  $-Z^{-2}$  blocks, where  $Z^{-1}$  is implemented by a pseudo-NMOS DFF and the  $-Z^{-2}$  by two DFFs following by an inverting block. 3-level DAC logic is defined in Table 4.1.

Figure 4.3: 1.5-bit DAC signal generation

Table 4.1: The logic used for DAC

| X | Y | Transmitted number    |

|---|---|-----------------------|

| 1 | 0 | +1                    |

| 0 | 1 | -1                    |

| 0 | 0 | 0                     |

| 1 | 1 | NA ( not transmitted) |

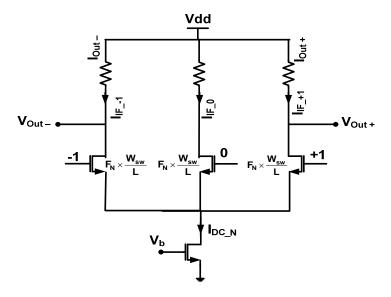

### 4.4 IF switching cell

As mentioned before, for each FIR current source there is an IF switch cell which consists of three NMOS devices out of which only one is ON (in saturation) and the other two are off at each time. The DC current of each tap from 1 to 20 are different and modulated by the FIR filter coefficients, therefore the DC current in the conducting device of the IF switches will be different for each tap. In order to maintain the same current density in the IF switches of all taps, the switches are scaled with currents or FIR coefficients. The unit size is designed to optimize for best operation point, allowing highest swing and high gm, and the multiples are used to scale the sizes according to the coefficients.

However there are two possibilities for current value in each tap, corresponding to the two standards. Since the IF switches are shared between WCDMA and WLAN modes, the average of the size needed in each mode is used to minimize the change in current density in the saturated NMOS's. Figure 4.4

Figure 4.4: The IF switch cell for N<sub>th</sub> tap

shows the  $N_{th}$  tap consisting of positive (+1), negative (-1) and dump current path (0) with device sizes scaled by  $F_N$  for the  $N_{th}$  tap as explained above.

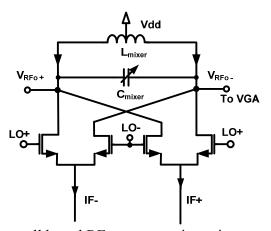

#### 4.5 Gilbert-cell Mixer

The up-conversion mixer is realized using a double-balanced fully differential Gilbert-cell mixer that offers low LO leakage to the output as shown in Fig. 4.5. In order to have an option for the WLAN band operation, a tunable LC load is designed with variable  $C_{\text{mixer}}$  and the fixed  $L_{\text{mixer}}$ .

Figure 4.5: The Gilbert-cell based RF up-conversion mixer

#### 4.6 Frequency Divider and Clock Buffer

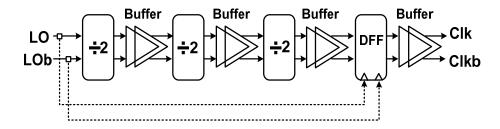

As explained in [1], in order to push the digital images out of the receiver bands, the LO frequency is chosen to be around 2GHz and the sampling frequency  $f_s$  is no less than but close to 250MHz. The on-chip clock of 250MHz is generated by the LO frequency divided down by 8. The frequency divider is shown in Fig. 4.6. It consists of three  $\div 2$  stages and refreshing buffers. The output of the last divider is re-clocked by the input signal at 2GHz. The last DFF is

placed next to the input LO to minimize the on-chip layout length and the delay as shown in the dashed line in Fig. 4.6. The clock buffer is designed to drive a large number of the digital gates. In order to achieve equal length for all the digital paths, the clock buffer layout is in a tree form.

Fig. 4.6: Frequency divider with division ratio of 8

#### 4.7 Summary

The IF to RF DAC presented in this chapter consists of a current-steering 3-level DAC, 1.5-bit digital IF switching cells, FIR filter and Gilbert-cell upconverter. Different form the traditional way of implementation of DAC following RF mixer and then RF band-pass filtering, it merges the DAC, mixer and the reconstruction filter into a single block to reduce circuit complexity and power consumption. The DAC design is based on the linearity requirement derived from Chapter 3. The design details of each individual sub-blocks including the 40-tap FIR filter, 3-level DAC input signal generation, 1.5-bit IF switching cells, RF mixer as well as the clock divider and buffer are demonstrated with the main focus on the design trade-offs. Also the design of IF to RF DAC provides an option for WLAN 802.11g application with different sets of WLAN FIR coefficients and tunable RF mixer load to potentially maximize the circuit

reuse.

The designed IF to RF upconverter with embedded FIR reconstruction filter is implemented using 0.18 $\mu$ m IBM7RF CMOS technology. It consumes approximately 67mA current from 1.8V DC supply and occupies about 0.61 $\mu$ m² dies area.

#### CHAPTER 5

#### DESIGN OF RF VARIABLE GAIN AMPLIFIER

According to W-CDMA standard, the base station should receive equal power from each other. Therefore, the transmitters need to be regulated based on the different locations and distances from the base station. The minimum 74dB dynamic range is demanded in the W-CDMA mobile transmitter standard [5]. The power control could be done entirely at the RF power amplifier (PA) stage, but it requires super linear and high power PA which makes not only the design of the RF PA extremely challenging but also less benefits on the power consumption and linearity (W-CDMA transmitter employs linear modulation scheme [32]). Instead, by distributing the 74dB power variation to the several blocks before the PA could actually relax the design requirements on the PA and result in a powerefficient transmitter. Therefore RF variable gain amplifier (VGA) becomes an essential block for W-CDMA transmitter to achieve the demanding powervariation task. In this work the required transmitter power control range can be achieved in two separate stages with 50dB from RF VGA and the rest from the sigma-delta IF stage. The design specifications for the RF VGA are listed in Table 5.1. Note that the 2.4GHz WLAN 802.11g band is also included in RF VGA design specifications. Since the WLAN 802.11g transmitter band is not far from W-CDMA transmit band and it requires less power variation compared to that of the W-CDMA, by adding some tunable circuits, one RF VGA can easily support two standards which could potentially be useful for multi-band multimode software defined transmitters.

Table 5.1: RF VGA design specifications

| Parameters                | Specifications                                              |  |

|---------------------------|-------------------------------------------------------------|--|

| Operation frequency bands | 1920 – 1980MHz (W-CDMA)<br>2400 – 2483.5MHz (WLAN 802.11g)* |  |

| Maximum output power      | 0dBm (with 5dB back-off)                                    |  |

| Power range               | -50dBm to 0dBm                                              |  |

| Power step                | 10 dB                                                       |  |

| Dynamic range             | 50dB from -40dB to 10dB                                     |  |

| Power step tolerance      | +/- 2dB                                                     |  |

| Temperature variation     | +/- 2dB                                                     |  |

| Output impedance          | 100 ohm matching to 50 ohm load using off-chip 2:1 balun.   |  |

<sup>(\*</sup> WLAN is optional.)

Recently many VGA designs have been reported [24]-[28]. The VGAs in [24]-[27] are realized using bipolar transistors (BJT) while the VGA in [28] is implemented in the CMOS technology. Except for the VGA in [4], which utilizes the so-called current-bleeding method, the implementations of the linear gain range are achieved unanimously by using variable  $g_m$  topology. By changing the bias current  $I_b$  of the input transistor or transistor pair, the transconductances  $g_m$  of these transistors are changed accordingly. Because the gain of the VGA is proportional to  $g_m$ , the gain variation is obtained by modulating the devices transconductances. In this approach, the key for a wide linear-in-dB gain range is to keep the BJTs operating in the active region and the CMOS transistors in the

subthreshold region. Indeed, when the transistors work in those regions, the bias current  $I_{b_i}$  can be generated by a variable voltage  $V_{ctrl}$  and follows an exponential relationship:

$$I_b \propto exp(V_{ctrl})$$

(5.1)

Note that  $g_m$  of the transistor is proportional to the bias current  $I_b$ . Therefore,  $g_m$  is proportional to  $exp(V_{ctrl})$  and the gain is linear with  $V_{ctrl}$  in the log scale. The advantages of this topology are the low supply voltage and the low power consumption. However, for high-speed applications, such as RF VGA at GHz range and beyond, the CMOS implementation does not perform well because of the poor  $f_t$  (MOSFET transition frequency ) of subthreshold MOS transistor. Therefore the CMOS variable  $g_m$  topology is only limited to the intermediate frequency (IF) applications.

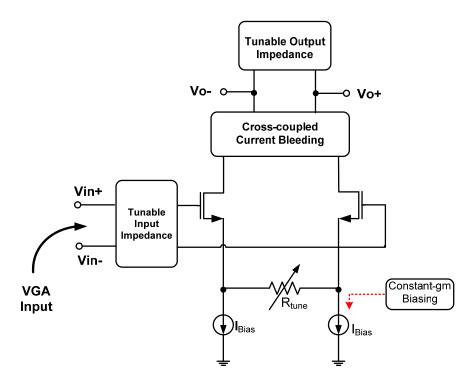

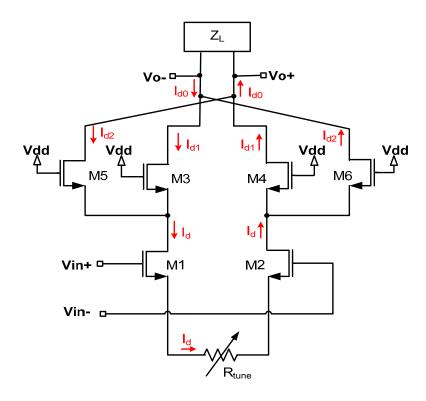

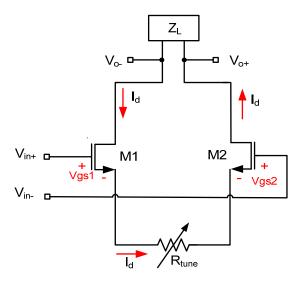

In order to meet specifications listed in Table 5.1 while keeping the design compact, a new CMOS RF VGA topology needs to be developed to support the specifications. In this work a single-stage discrete-power-step VGA for two frequency bands is proposed. The design strategy is shown in Fig. 5.1.

As the RF VGA is a part of a digital transmitter, the gain-control signals are preferred to be done in digital domain to take advantage of digital signal processing in the baseband. In order to utilize one VGA for two frequency bands rather than two standalone variable gain amplifiers, switches are introduced in the input and output tunable LC networks to adaptively select the impedance values to match desired center frequencies, which is a similar scenarios used in [29]. To achieve a wide dynamic range, the VGA needs to adaptively attenuate large input

Figure 5.1: VGA design strategy

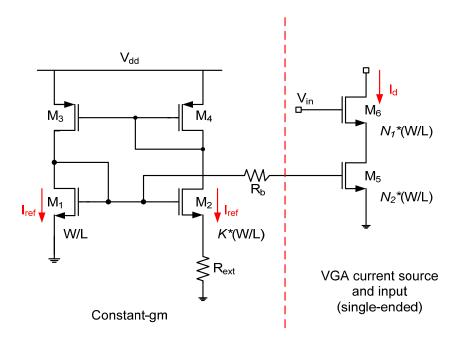

signal coming from the RF DAC/Mixer. This can be done by using resistor degeneration combined with current bleeding technique. Resistor degeneration is a common approach in VGA design to boost linearity. It can be realized by using MOS transistor, where the resistor value is controlled by the input signal at the gate [25] [30]. However, the control signal is analog. In this work a switchable poly resistor bank  $R_{tune}$  is adopted to replace the linear MOS resistors. In this way, the resistor value is controlled by the digital signals applied to the switches. The current bleeding technology is another attractive way to linearly attenuate the input signal. It has been reported in [22][24][28]. However, the control signals in [22][24][28] are still in the analog domain. In order to realize gain control signals all digital, switches are again introduced to selectively turn on and off transistor

pairs to control the amplitude of the output signal. Ideally the resistor degeneration approach should provide a large gain variation, however, in real circuitry implantation, it can only achieve limited attenuation due to the parasitics from the drain of the current source  $I_{Bias}$  and the switches used in the  $R_{tune}$ . By combining the switchable current bleeding and the resistor degeneration together, the desired attenuation can be achieved while the gain control signals are performed completely in the digital domain. As mentioned in Table 5.1, the VGA should not be sensitive to temperature variation, and constant-gm biasing [12] is famous for its robustness in temperature and simple to implement, therefore it has been used to bias the current source  $I_{Bias}$  in Fig. 5.1.

In summary, the design strategies of the proposed RF VGA can be highlighted as follows:

- 1) The operation frequency of W-CDMA band or WLAN band is determined by the input and output tunable impedances.