# Designing Low Cost Error Correction Schemes for Improving Memory Reliability

by

Hsing-Min Chen

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved April 2017 by the Graduate Supervisory Committee:

Chaitali Chakrabarti, Chair Trevor Mudge Carole-Jean Wu Umit Ogras

ARIZONA STATE UNIVERSITY

May 2017

#### ABSTRACT

Memory systems are becoming increasingly error-prone, and thus guaranteeing their reliability is a major challenge. In this dissertation, new techniques to improve the reliability of both 2D and 3D dynamic random access memory (DRAM) systems are presented. The proposed schemes have higher reliability than current systems but with lower power, better performance and lower hardware cost.

First, a low overhead solution that improves the reliability of commodity DRAM systems with no change in the existing memory architecture is presented. Specifically, five erasure and error correction (E-ECC) schemes are proposed that provide at least Chipkill-Correct protection for x4 (Schemes 1, 2 and 3), x8 (Scheme 4) and x16 (Scheme 5) DRAM systems. All schemes have superior error correction performance due to the use of strong symbol-based codes. In addition, the use of erasure codes extends the lifetime of the 2D DRAM systems.

Next, two error correction schemes are presented for 3D DRAM memory systems. The first scheme is a rate-adaptive, two-tiered error correction scheme (RATT-ECC) that provides strong reliability (10<sup>10</sup>x reduction in raw FIT rate) for an HBM-like 3D DRAM system that services CPU applications. The rate-adaptive feature of RATT-ECC enables permanent bank failures to be handled through sparing. It can also be used to significantly reduce the refresh power consumption without decreasing the reliability and timing performance.

The second scheme is a two-tiered error correction scheme (Config-ECC) that supports different sized accesses in GPU applications with strong reliability. It addresses the mismatch between data access size and fixed sized ECC scheme by designing a product code based flexible scheme. Config-ECC is built around a core unit designed for 32B access with a simple extension to support 64B and 128B accesses. Compared to fixed 32B and 64B ECC schemes, Config-ECC reduces the failure in time (FIT)

rate by 200x and 20x, respectively. It also reduces the memory energy by 17% (in the dynamic mode) and 21% (in the static mode) compared to a state-of-the-art fixed 64B ECC scheme.

# DEDICATION

To my parents

#### ACKNOWLEDGMENTS

I wish to express my gratitude to my advisor and mentor, Dr. Chaitali Chakrabarti, who has patiently taught me to do research, speak and write. I cannot remember how many weekends we have worked together to discuss my research. I am deeply indebted for her guidance, encouragement and support throughout my graduate study.

I wish to thank Dr. Trevor Mudge, Dr. Carole-Jean Wu and Dr. Umit Ogras for serving on my thesis committee, and for their insightful comments in improving my research. Dr. Mudge brought me into the DARPA project. I do appreciate his feedback during our weekly meetings. I would also like to thank Dr. Wu for her critical comments. Her tough words and critical thinking always pushed me to improve my work.

I would like to thank all my collaborating researchers, Suprect Jeloka, Nilmini Abeyratne and Byoungchan Oh, at the University of Michigan as well as Akhil Arunkumar and Shin-Ying Lee at Arizona State University. I am also grateful to DARPA, the National Science Foundation and the School of Electrical, Computer and Energy Engineering at ASU for funding my graduate study.

I wish to thank my colleagues in the Low Power Systems Lab, Chengen Yang, Lifeng Miao, Ming Yang, Siyuan Wei, Madhu Vasudevan, Manqing Mao, Asha Sasikumar, Jian Zhou, Vamsi Chagari Reddy, Jaideep Gour, Jiang Xiang and Shunyao Wu. I have learnt a lot from them. It is because of them that the Low Power Systems Lab was a great place to work in. I also want to thank my girl friend, Rui Liu, for her endless support and care.

I wish to thank all my friends and roommates in Arizona. Without them I would not have such colorful memories to cherish. Without them I may not have survived the PhD program! Finally and most importantly, I would like to thank my parents. I am grateful to them for fostering my interests in science and engineering. Their unconditional love and sustained support has been and will always be the force with me.

# TABLE OF CONTENTS

|      |      |         | P                                     | age |

|------|------|---------|---------------------------------------|-----|

| LIST | ОБ Л | TABLES  | S                                     | X   |

| LIST | OF F | TIGURI  | ES                                    | xii |

| СНАІ | PTER | 2       |                                       |     |

| 1    | INT  | RODU    | CTION                                 | 1   |

|      | 1.1  | Motiva  | ation                                 | 1   |

|      | 1.2  | 2D DI   | RAM Reliability                       | 2   |

|      | 1.3  | 3D DI   | RAM Reliability                       | 5   |

|      |      | 1.3.1   | ECC For 3D DRAM In CPU Systems        | 6   |

|      |      | 1.3.2   | ECC For 3D DRAM In GPU Systems        | 8   |

|      | 1.4  | Disser  | tation Organization                   | 11  |

| 2    | BAC  | CKGRC   | OUND                                  | 12  |

|      | 2.1  | DRAN    | M Memory Systems                      | 12  |

|      |      | 2.1.1   | 2D Commodity DRAM Architecture        | 12  |

|      |      | 2.1.2   | 3D DRAM Memory Architecture           | 13  |

|      | 2.2  | DRAN    | M Error Characteristics               | 16  |

|      |      | 2.2.1   | 2D Commodity DRAM Errors              | 16  |

|      |      | 2.2.2   | 3D Die-Stacked DRAM Errors            | 18  |

|      | 2.3  | Existin | ng ECC Mechanisms                     | 19  |

|      |      | 2.3.1   | Existing Schemes in 2D DRAM           | 19  |

|      |      | 2.3.2   | Existing Schemes In 3D DRAM           | 21  |

|      | 2.4  | Error   | Logging Architecture                  | 22  |

| 3    | 2D 1 | DRAM    | ECC SCHEMES                           | 24  |

|      | 3.1  | Propo   | sed E-ECC Schemes For x4 DRAM Systems | 25  |

|      |      | 3.1.1   | E-ECC Scheme 1 - x4 DRAM System       | 25  |

| СНАРТЕР | }      | I                                                 | Page |

|---------|--------|---------------------------------------------------|------|

|         | 3.1.2  | E-ECC Scheme 2 - x4 DRAM System                   | 26   |

|         | 3.1.3  | E-ECC Scheme 3 - x4 DRAM System                   | 28   |

| 3.2     | Propo  | sed E-ECC Schemes For x8 DRAM Systems             | 31   |

|         | 3.2.1  | E-ECC Scheme 4 - x8 DRAM System                   | 31   |

| 3.3     | Propo  | sed E-ECC Schemes For x16 DRAM Systems            | 33   |

|         | 3.3.1  | E-ECC Scheme 5 - x16 DRAM System                  | 33   |

| 3.4     | Synthe | esis Results                                      | 34   |

| 3.5     | Evalua | ation                                             | 38   |

|         | 3.5.1  | Workloads                                         | 38   |

|         | 3.5.2  | Results And Analysis                              | 39   |

|         | 3.5.3  | Reliability Analysis                              | 44   |

|         | 3.5.4  | Overhead Comparison                               | 46   |

| 3.6     | Summ   | ary                                               | 48   |

| 4 3D I  | DRAM   | ECC SCHEMES FOR CPU                               | 49   |

| 4.1     | Overv  | iew Of RATT-ECC                                   | 49   |

|         | 4.1.1  | Strategies For Handling 3D DRAM Faults            | 50   |

|         | 4.1.2  | Design Of Tier-1 And Tier-2 Codes                 | 51   |

| 4.2     | Detail | s Of RATT-ECC                                     | 53   |

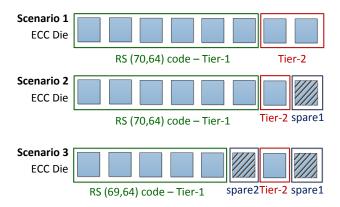

|         | 4.2.1  | Scenario 1 - No Banks Are Marked As Faulty        | 53   |

|         | 4.2.2  | Scenario 2 - 1 Data Bank Is Marked As Faulty      | 58   |

|         | 4.2.3  | Scenario 3 - 2 Banks Are Marked As Faulty         | 59   |

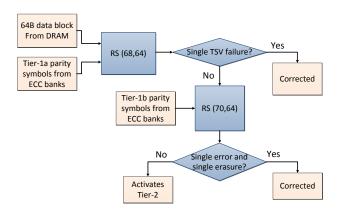

|         | 4.2.4  | Correction Of Errors Due To Permanent TSV Failure | 60   |

| 4.3     | Evalua | ation                                             | 61   |

|         | 4.3.1  | Timing Performance Analysis                       | 62   |

| СНАР | TER  |         | ]                                                     | Page  |

|------|------|---------|-------------------------------------------------------|-------|

|      |      | 4.3.2   | Reliability Comparison                                | . 69  |

|      |      | 4.3.3   | Hardware Overhead Of RATT-ECC                         | . 72  |

|      | 4.4  | Summ    | ary                                                   | . 74  |

| 5    | 3D I | ORAM    | ECC SCHEMES FOR GPU                                   | . 75  |

|      | 5.1  | Motiva  | ation For An ECC Design Supporting GPU's Varying Data |       |

|      |      | Fetch   | Sizes                                                 | . 75  |

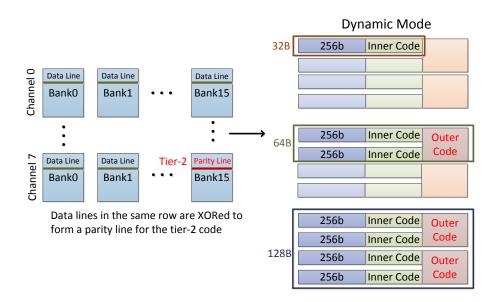

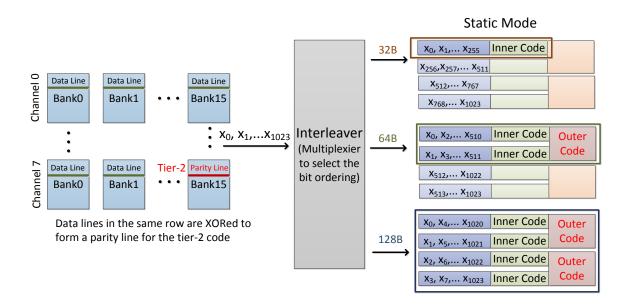

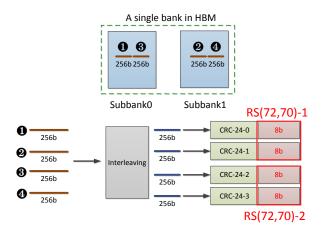

|      | 5.2  | Overv   | iew Of Config-ECC                                     | . 79  |

|      |      | 5.2.1   | Design Of Tier-1 Code                                 | . 79  |

|      |      | 5.2.2   | Tier-2 Code                                           | . 82  |

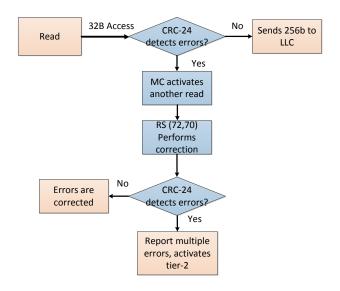

|      | 5.3  | Details | s Of 32B Config-ECC                                   | . 83  |

|      |      | 5.3.1   | Design Of the Tier-1 Inner Code                       | . 83  |

|      |      | 5.3.2   | Design Of Tier-1 Outer Code                           | . 85  |

|      |      | 5.3.3   | Error Correction & Detection                          | . 86  |

|      | 5.4  | Extens  | sions Of Config-ECC                                   | . 87  |

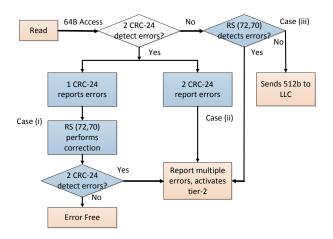

|      |      | 5.4.1   | Dynamic Mode Protection                               | . 87  |

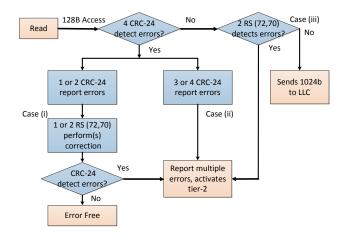

|      |      | 5.4.2   | Static Mode Protection                                | . 89  |

|      | 5.5  | Metho   | dology                                                | . 90  |

|      |      | 5.5.1   | Setup For Reliability Evaluation                      | . 92  |

|      |      | 5.5.2   | System Simulation Infrastructure                      | . 93  |

|      |      | 5.5.3   | HBM Energy Modeling                                   | . 94  |

|      | 5.6  | Result  | s and Analysis                                        | . 95  |

|      |      | 5.6.1   | Reliability Comparison                                | . 95  |

|      |      | 5.6.2   | Energy Comparison                                     | . 98  |

|      | 5.7  | Summ    | ary                                                   | . 102 |

| СНАРТЕ | ER       | P                         | age |

|--------|----------|---------------------------|-----|

| 6 CC   | ONCLUS   | IONS                      | 103 |

| 6.1    | 2D DF    | RAM Reliability           | 103 |

| 6.2    | 2 3D DF  | RAM Reliability           | 104 |

|        | 6.2.1    | CPU Systems               | 104 |

|        | 6.2.2    | GPU Systems               | 105 |

| 6.3    | B Future | e Work                    | 106 |

| REFERE | NCES     |                           | 107 |

| APPEND | XI       |                           |     |

| A DE   | ECODING  | G ALGORITHMS FOR E-ECC    | 114 |

| B DE   | ECODING  | G ALGORITHMS FOR RATT-ECC | 118 |

# LIST OF TABLES

| Table |                                                                   | Page |

|-------|-------------------------------------------------------------------|------|

| 2.1   | DRAM Fault Modes in Hopper                                        | . 17 |

| 3.1   | Synthesis Results Using A 28nm Library - Latency                  | . 36 |

| 3.2   | Synthesis Results Using A 28nm Library - Power                    | . 37 |

| 3.3   | Synthesis Results Using A 28nm Library - Area                     | . 37 |

| 3.4   | Simulation System Parameters                                      | . 38 |

| 3.5   | Sequential And Multiprogrammed Workloads                          | . 39 |

| 3.6   | Memory Configurations Of The Five E-ECC Schemes                   | . 43 |

| 3.7   | Error Detection And Correction Comparison                         | . 46 |

| 3.8   | Overhead Comparison                                               | . 47 |

| 4.1   | Error Handling Performance Of The Different Decoding Cases of RS  |      |

|       | (70,64)                                                           | . 55 |

| 4.2   | Simulation Configuration                                          | . 61 |

| 4.3   | Workloads                                                         | . 63 |

| 4.4   | The Coverage Of Tier-1a, Tier-1b And Tier-2 Parity For Three Sce- |      |

|       | narios. Each Block Is Of Size 64B                                 | . 63 |

| 4.5   | Comparison Of The Error Handling Performance Of Tier-1 Codes Used |      |

|       | In The Existing Schemes                                           | . 64 |

| 4.6   | FIT Analysis                                                      | . 64 |

| 4.7   | Number Of DRAM Cell Retention Errors As A Function Of Refresh     |      |

|       | Interval In A 60nm Process; The Default Refresh Interval Is 64ms  | . 67 |

| 4.8   | Synthesis Results Of Existing ECC Schemes                         | . 73 |

| 5.1   | GPU And HBM System Configuration                                  | . 91 |

| 5.2   | Benchmarks For Config-ECC Energy Evaluation                       | . 93 |

| Table |                                                                   | Page |

|-------|-------------------------------------------------------------------|------|

| 5.3   | The Error Protection Coverage For 32B Config-ECC And The Existing |      |

|       | Schemes                                                           | . 96 |

| 5.4   | The Error Protection Coverage For 64B Config-ECC And The Existing |      |

|       | Schemes                                                           | . 97 |

| 5.5   | The Final FIT Rate Of Config-ECC Schemes                          | . 98 |

# LIST OF FIGURES

| Figure | Pa                                                                | age |

|--------|-------------------------------------------------------------------|-----|

| 2.1    | Logical View Of A DRAM Based Memory System                        | 12  |

| 2.2    | 32B vs. 64B Accesses in HBM2 (Pseudo Channel Mode)                | 14  |

| 2.3    | 3D HBM-Like Structure With An ECC Die                             | 15  |

| 2.4    | 512b or 64 Symbols Are Read From A Bank In A Data Die             | 16  |

| 3.1    | Overview Of The Decoding Algorithm For E-ECC Scheme 1             | 26  |

| 3.2    | E-ECC Scheme 2. x4 DRAM Access Pattern Of Two Ranks               | 27  |

| 3.3    | E-ECC Scheme 2. Overview Of The Decoding Algorithm                | 27  |

| 3.4    | E-ECC Scheme 3. x4 DRAM Access Pattern Of One Rank                | 30  |

| 3.5    | E-ECC Scheme 3. Overview Of The Decoding Algorithm                | 30  |

| 3.6    | E-ECC Scheme 4. x8 DRAM Access Pattern                            | 31  |

| 3.7    | E-ECC Scheme 5. x16 DRAM Access Pattern                           | 33  |

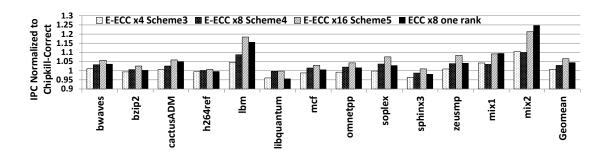

| 3.8    | IPC Performance Of Sequential And Multiprogrammed Applications.   |     |

|        | Schemes 1 And 2 Have The Same IPC Performance As Chipkill-Correct |     |

|        | (Baseline). LOT-ECC And Multi-ECC Have Performance Comparable     |     |

|        | To ECC x8 One Rank And V-ECC Has Performance Comparable To        |     |

|        | E-ECC x8 Scheme 4                                                 | 40  |

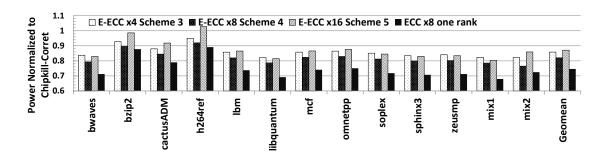

| 3.9    | Power Consumption Of Sequential And Multiprogrammed Workloads     |     |

|        | Normalized To Chipkill-Correct. Schemes 1 And 2 Have The Same     |     |

|        | Power Performance As Chipkill-Correct (Baseline). LOT-ECC And     |     |

|        | Multi-ECC Have Performance Comparable To ECC x8 One Rank And      |     |

|        | V-ECC Has Performance Comparable To E-ECC x8 Scheme 4             | 42  |

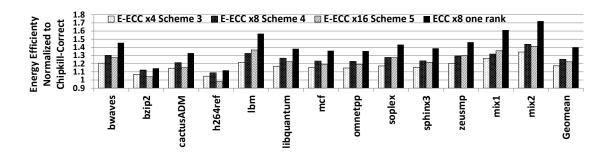

| 3.10 | Energy Efficiency Of Different E-ECC Schemes. Schemes 1 And 2     |    |

|------|-------------------------------------------------------------------|----|

|      | Have The Same Energy Efficiency Performance As Chipkill-Correct   |    |

|      | (Baseline). LOT-ECC And Multi-ECC Have Performance Comparable     |    |

|      | To ECC x8 One Rank And V-ECC Has Performance Comparable To        |    |

|      | E-ECC x8 Scheme 4.                                                | 44 |

| 4.1  | RATT-ECC Overview                                                 | 50 |

| 4.2  | Scenario 1: Flowchart For Accessing Data Cache Line, Tier-1 Code  |    |

|      | And Tier-2 Code                                                   | 53 |

| 4.3  | 3 Scenarios Of RATT-ECC                                           | 54 |

| 4.4  | Decoding Flowchart Of Erasure And Error Correction Mode Of RS     |    |

|      | (70,64) Code For Handling Errors Due To A Permanent TSV Failure   | 60 |

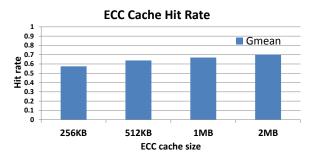

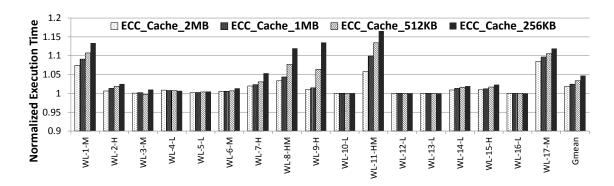

| 4.5  | Hit Rate Of Different Sized ECC Cache                             | 66 |

| 4.6  | Normalized Execution Time For Different ECC Cache Sizes           | 66 |

| 4.7  | Number Of Additional Error Corrections For 8GB DRAM When The      |    |

|      | Refresh Interval Is Increased.                                    | 68 |

| 4.8  | Power Reduction Of 8GB Memory For Different Refresh Intervals     | 69 |

| 4.9  | Power Reduction Of 8GB To 64GB Memory For Different Refresh In-   |    |

|      | tervals                                                           | 69 |

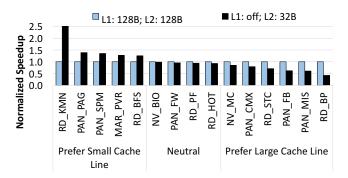

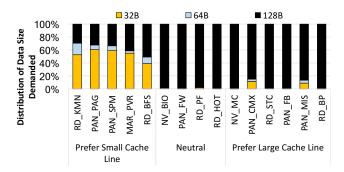

| 5.1  | The Normalized Execution Time Speedup With Different Two Cache    |    |

|      | Configurations: 128B Cache Line Size For Both L1 And L2 Caches    |    |

|      | Versus L1 Cache Disabled And 32B Cache Line Size For The L2 Cache |    |

|      | (Provided By Shin-Ying Lee)                                       | 77 |

| 5.2  | The Distribution Of Number Of Bytes Referenced During A Cache     |    |

|      | Line's Lifetime (Provided By Shin-Ying Lee)                       | 77 |

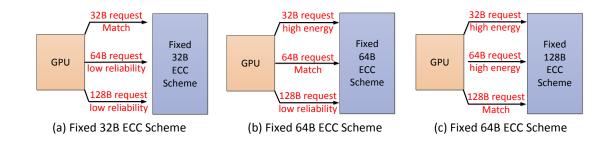

| 5.3 | Interaction Between Different GPU Access Request Sizes And Fixed |    |

|-----|------------------------------------------------------------------|----|

|     | Sized ECC Schemes                                                | 78 |

| 5.4 | Overview Of Config-ECC In The Dynamic Mode                       | 80 |

| 5.5 | Overview Of Config-ECC In The Static Mode                        | 80 |

| 5.6 | Decoding Flowchart for 32B Access                                | 84 |

| 5.7 | Decoding Flowchart For 64B Access                                | 88 |

| 5.8 | Block Diagram Of 128B Access: Static Mode                        | 89 |

| 5.9 | Decoding Flowchart For 128B Access: Static Mode                  | 92 |

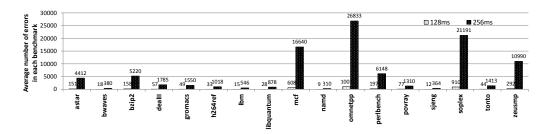

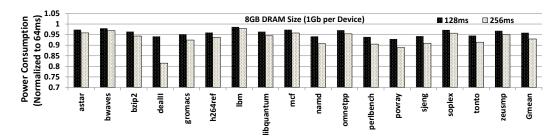

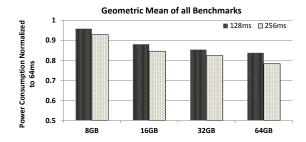

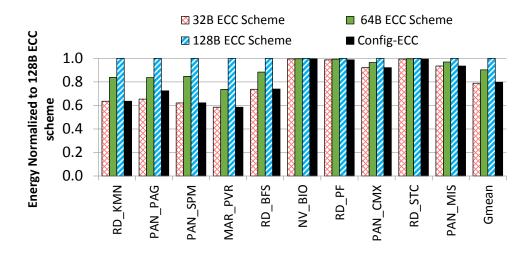

5.10 Energy Comparison Of The Competing Schemes When Operating In

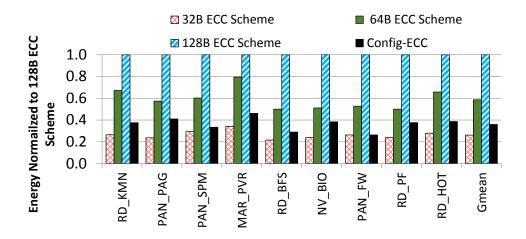

5.11 Energy Consumption Of The Competing Schemes When Operating In

The Static Operation Mode......101

Page

Figure

## Chapter 1

#### INTRODUCTION

#### 1.1 Motivation

In large scale computing systems, guaranteeing the reliability of its memory system is a major challenge. More than 40% of hardware related failures are attributed to errors in memory systems [1]. These errors cause computing systems to malfunction and also lead to serious security vulnerabilities [2]. To make it worse, due to the scaling down and the high density of memory cells, the number of errors is projected to increase in the future.

In this dissertation, we propose schemes to improve the reliability of both 2D dynamic random access memory (DRAM) and 3D DRAM systems. 2D DRAM system is used as main memory in most computer systems. Unfortunately, these systems are vulnerable to different kinds of faults (e.g. hard, intermittent or random) [3,4]. These faults manifest as single bit errors, multiple errors along a row and/or along a column of a chip and even whole chip failure. Error correction coding (ECC) [5] schemes are typically used to deal with DRAM errors. Designing an ECC code with low storage overhead and good error correction performance is quite a challenge.

2D DRAM has the advantages of high density, high capacity and low cost but its performance is limited by memory latency and bandwidth. 3D die-stacked DRAM is a promising solution to improve the system performance [6] and reduce the power consumption. It can provide higher bandwidth, lower power consumption, lower latency and has smaller footprint compared to 2D DRAM. There are several prototypes for 3D DRAM, including high bandwidth memory (HBM) [7], hybrid memory cube

(HMC) [8] and Octopus from Tezzaron [9]. However, 3D DRAM suffers from serious reliability issues due to higher density and thermal issues. Furthermore, since a single data line is not striped across multiple chips like 2D DRAM, it increases the difficulty of designing a strong ECC scheme. Also, through-silicon-via (TSV) failures occur only in the 3D DRAM structure and add to the complexity. In the rest of this chapter, we briefly describe the proposed low cost, low overhead and strong ECC schemes for 2D and 3D DRAM memory systems that improve their reliability without degrading their performance.

### 1.2 2D DRAM Reliability

Most computer systems use dynamic random access memory (DRAM) as main memory. As the size of DRAM in computer systems increases, DRAM reliability becomes a serious concern. The traditional single bit error correction and double bit error detection (SEC-DED) code is no longer strong enough to guarantee the memory reliability.

High performance servers are typically expected to have Chipkill-Correct level protection, that is the ability to correct errors due to failures of a DRAM chip with 12.5% storage overhead [10,11]. Chipkill-Correct was first implemented by striping data across multiple chips so that a single error correction and double error detection (SEC-DED) code could be used to correct errors due to a chip failure [10]. The bit-level Chipkill-Correct code had high power consumption and low system performance and so symbol-based Chipkill-Correct was proposed for x4 DRAM systems in [12,13]. This scheme activated 36 chips across two ranks for every memory access and thus also had high power consumption and lower timing performance.

To reduce the power consumption, many systems moved to x8 or x16 DRAMs, which activate fewer chips per memory access. For instance, V-ECC [14] activates

18 x8 chips across two ranks while LOT-ECC [15] and Multi-ECC [16] only activate nine chips per x8 rank. Although LOT-ECC and Multi-ECC can reduce the memory power by an average of more than 25% compared to Chipkill-Correct, they cannot fully correct a chip failure at run time.

In order to activate fewer chips and maintain high reliability, many systems employ two-tier schemes [14–18], where the first tier is used for error detection and the second tier is used for error correction. For example, V-ECC [14] uses two check symbols in the first tier to perform error detection and the third check symbol in the second tier to perform error correction. The second tier is usually cached to reduce the read latency for error correction and the write frequency for ECC updates.

Existing schemes such as those in [15,16] also rely on replacement of faulty chips to extend the lifetime of the DRAM memory systems. Some commercial systems use memory sparing or bit-steering [16,19,20] to re-route the faulty bits or re-route data from a faulty chip to a healthy chip. This not only reduces the usable physical memory size but also increases the overhead required to perform re-routing or mapping.

In this work we propose a very different approach to providing at least Chipkill-Correct error protection for commodity DRAM systems. Our approach is based on the use of stronger symbol based codes which are chosen to handle the constraints of different memory systems. Use of a stronger code adds very little overhead to existing systems. Our synthesis results in 28nm node show that the decoding latencies of these codes are very small and do not affect the DRAM timing performance. Moreover, unlike the existing multi-tiered schemes, our schemes do not require extra memory read/write operations to access data or to do error correction.

Furthermore, instead of employing chip sparing to increase the lifetime of memory systems, we make use of erasure correction, where an erasure is defined as an error whose location is known. We utilize the machine check architecture (MCA) [20, 21]

to record the error information of each chip. Once the number of errors in a certain chip increases beyond a threshold, this chip is marked as faulty and errors due to this chip are treated as erasures.

We present five erasure and error correction (E-ECC) schemes that provide at least Chipkill-Correct reliability for x4, x8 and x16 DRAM systems. All the proposed E-ECC schemes can correct errors due to a chip failure on the fly and can correct one additional random error when the chip is marked as faulty. In order to demonstrate that our proposed schemes have low cost and low overhead, we synthesize all decoding units using industrial 28nm library to obtain the corresponding latency, area and power results. In addition, we analyze the tradeoffs between reliability and system performance (timing, power and energy) of these proposed schemes and compare them to the existing competing schemes.

Overall, we make the following key contributions in the design of reliable 2D DRAM systems:

- For x4 DRAM systems, we present three schemes that all have 12.5% storage overhead but differ in the number of ranks being activated (one or two). The specific ECC codes used in these three schemes are rotational (144,128) code over GF(2<sup>4</sup>) and RS (36,32) code over GF(2<sup>8</sup>). The schemes that activate two ranks per memory access have lower timing, power and energy performance but higher reliability compared to the one that activates only one rank.

- For x8 DRAM systems, we propose a scheme which is also based on the RS (36,32) code over GF(2<sup>8</sup>). It accesses two ranks per memory access and has the lowest power consumption and highest energy efficiency among all five schemes.

- For x16 DRAM systems, we propose a scheme which is based on the RS (20,16) code over  $GF(2^8)$ . This scheme activates two ranks per memory access, has

storage overhead of 25% but has the highest timing performance among all the schemes.

This work appeared in ACM MEMSYS Conference [22] and IEEE Transactions on Computers [23].

### 1.3 3D DRAM Reliability

The 3D die-stacked DRAM is an excellent candidate for high performance computer systems. It has lower access latency, lower power consumption and higher bandwidth [6, 24]. In this work, we consider an HBM-like structure where multiple dies are stacked on top of the logic die; stacking is achieved by the use of through silicon vias (TSV).

Unfortunately, 3D DRAM is likely to be less reliable than 2D DRAM because of additional errors due to its higher integration density. The increase of errors in 2D DRAM due to higher density has been well documented in [3,4,25,26]. The 2D DRAM errors that were due to transient and permanent single bit, column, row and bank failures are expected to be present in 3D DRAM as well. In addition, 3D DRAM will incur errors caused by TSV failures. Thus, designing a reliable memory system using an error-prone 3D die-stacked DRAM is quite a challenge.

Added to this challenge is the fact that in a 3D DRAM (such as HBM), data block from a lower level cache is stored in a single bank and not striped across multiple banks as in 2D DRAM. While this results in lower power and higher performance as shown in [27,28], it makes the design of a reliable system even more challenging. For instance, if a bank fails, an entire cache line is corrupted. Traditional ECC schemes for 2D DRAMs such as Chipkill-Correct [11], virtualized-ECC [14], LOT-ECC [15] and Multi-ECC [16] were all based on data being striped across different banks. Hence, these schemes cannot be extended to handle 3D DRAM.

In recent years, several schemes have been proposed for improving the reliability of 3D DRAM. These include Subarraykill [29], Resilient-DRAM-Caches [30], Efficient-RAS [28], Citadel [27] and Parity-Helix [31]. Subarraykill [29] proposes an ECC scheme for the specialized Tezzaron Octopus structure, which allows for the data to be striped across several subarrays. The ECC design in [30] focuses on the protection of the last level cache; the single bit error correction code and small size of cyclic redundancy code (CRC) [5] are not strong enough for 3D DRAM memory. Citadel [27] and Efficient-RAS [28] are two contemporary systems that have been designed for HBM-like memory. Both use two tiered schemes, where the first tier is used to only detect [27], or detect as well as correct [28], and the second tier is used to correct errors detected but not corrected by the first tier. Efficient-RAS [28] uses symbol based rotational code to correct errors due to small granularity faults while Citadel [27] uses CRC-32 to detect errors and relies on tier-2 code to correct all errors. Since small granularity faults account for 70% of all faults [26], this can affect the timing performance. Parity-Helix [31] focuses on the tier-2 code design where the ECC parity bits are twisted so that the system can recover from errors due to a single dimensional failure in a multi-dimensional memory system.

### 1.3.1 ECC For 3D DRAM In CPU Systems

In this work, we propose rate-adaptive two-tiered error correction scheme (RATT-ECC) to deal with errors due to transient and permanent 3D failures in an HBM-like 3D DRAM system that services CPUs. Here, the memory is organized into 8 data dies and one additional die is used to store the error correction (ECC) bits. CPU systems typically have data access size of 64B and so the proposed ECC scheme is optimized for 64B access.

In RATT-ECC, the tier-1 code is based on a Reed-Solomon (RS) code [5] to provide strong error detection and correction capability. The strong detection capability reduces error leaks and the strong error correction capability decreases the frequency of tier-2 activation. RATT-ECC can correct errors due to all small granularity faults such as single bit, column or TSV failures by using tier-1 code. It needs tier-2 code only for correcting errors due to large granularity faults such as row or bank failures. RATT-ECC uses RS (70,64) as the tier-1 code. This code can be used to correct one symbol error and detect five symbol errors. Since the undetected error probability of tier-1 code is as low as  $2.3 \cdot 10^{-10}$ , almost all errors can be corrected by the tier-2 code. The tier-1 code can also be used as an erasure code and errors due to permanent TSV failure can be easily corrected.

Furthermore, RATT-ECC has a mechanism to free up banks in the ECC die to handle faulty data banks. It alters the rate of tier-1 and tier-2 codes so that these codes need less parity storage allowing for 1 or 2 spare banks. Specifically, by puncturing RS (70,64) code to RS (69,64) code, it frees up one ECC bank since RS (69,64) requires five ECC banks to store its parity symbols. A second ECC bank can be freed up by XORing the tier-2 parity symbols that were originally stored in two ECC banks. Thus RATT-ECC can provide for a highly reliable 3D DRAM system that is plagued with all types of faults.

Overall, we make the following key contributions in the design of a reliable 3D DRAM system that services CPUs:

• Design of a rate-adaptive two-tiered ECC scheme with a total storage overhead of 12.5% to correct errors due to small and large granularity faults. The strong correction capability of tier-1 code reduces the number of activations of tier-2 code and the strong detection capability of tier-1 code avoids substantial error leaks. Overall, the raw failure-in-time (FIT) rate is reduced by more than 10<sup>10</sup>x.

- The rate adaptive feature of tier-1 code and tier-2 code allows for up to two spare banks in the ECC die. Thus the memory system can reliably function even after two data banks are marked faulty with very little overhead.

- The erasure correction capability of the tier-1 code is utilized to handle permanent TSV failures with no performance overhead.

- The synthesis results in 28nm technology show that the proposed tier-1 code has very small overhead in area, power and latency. Simulations on SPEC2006 benchmark shows that the timing performance drops by less than 2% compared to the baseline scheme with no ECC.

This work appeared in ACM Transactions on Architecture and Code Optimization [32].

## 1.3.2 ECC For 3D DRAM In GPU Systems

Graphics processing units (GPUs) play an increasingly significant role in high performance computers. 3D DRAMs, e.g., high bandwidth memory (HBM) [33], are projected to be widely adopted in GPU memory systems in the near future. In fact, 3D DRAMs have already been applied in some commercial GPU products, such as Nvidia Tesla P100 [34] and AMD Radeon R9 FURY X GPU cards [35]. In this work, we assume that 3D DRAM is organized into 8 dies, where each die holds both data bits and ECC bits.

Designing an ECC scheme for GPU memory systems is more challenging than for CPUs. The data fetch granularity from GPUs can vary and so designing an ECC scheme for fixed sized data access is sub-optimal. Current GPU products support different cache line sizes. For example, AMD GPUs, such as the RADEON series, adopt 64B as the cache line size [36], whereas Nvidia uses 128B L2 cache line size

in many of their GPU products. In some GPU products, the L2 cache line size can be statically configured to operate in 2 different modes (32B or 128B) before a GPU kernel is launched [37]. This is proposed with compiler level analysis to fully exploit the varying degree of spatial locality in GPGPU applications. Furthermore, many recent studies [38,39] have shown that GPGPU applications exhibit mixed locality data access patterns over application execution. Therefore, a lot of designs have been proposed to dynamically predict and accommodate varying cache line sizes for the L1 cache [39] as well as for the L2 cache [38].

Traditionally, ECC algorithms used in DRAMs were optimized for fixed sized data accesses. Examples include CRC-16 for 32B accesses in [33], symbol-based code for 64B accesses in [28, 32]. However, applying an ECC scheme that is optimized for a single data access size leads to suboptimal memory reliability or higher energy consumption for the other data access sizes. For instance, an ECC algorithm optimized for 64B access leads to additional energy consumption if the GPU data fetch size is 32B. Alternatively, an ECC algorithm optimized for 32B data results in lower reliability compared to one that results in been designed for 64B data. Clearly, to better support the diversity of cache configurations in GPUs and the performance feature of the variable data fetch granularity runtime support for future GPUs, there is a strong need to develop an adaptive and flexible ECC scheme.

In this work, we propose Config-ECC, an ECC scheme that not only supports a diverse set of cache hierarchy configurations in different GPU cards in the static mode but is also designed to handle variable data fetch granularities at runtime in the dynamic mode with strong reliability and/or low energy consumption. Config-ECC is based on a two-tiered ECC code: The tier-1 code is a product code [5] that has strong error detection and correction capabilities. It can correct errors due to small granularity faults (single bit, column, and TSV failures) and detect errors with large

granularity fault (row or bank failures) with very low silent data corruption rate. The tier-2 code, which is based on an XOR structure and stored in the data banks, is launched for correcting errors due to large granularity faults.

Config-ECC is built around a core 32B ECC scheme that can be easily extended to support 64B and 128B accesses. The product code structure of Config-ECC helps address the mismatch between data access size and fixed size ECC scheme. Basically, the inner code is optimized to have very strong detection capability for 32B access and the combination of inner code and outer code provides for very strong reliability for 64B access. Config-ECC improves the silent data corruption rate (SDC) by 200 times compared to the 32B ECC scheme in the HBM standard and by 20 times compared to the latest 64B ECC schemes [27,32]. For applications that prefer small cache line size (32B), Config-ECC has significantly lower energy consumption compared to 64B and 128B ECC schemes and also provide stronger reliability than that of a fixed 32B ECC scheme.

Our main contributions are as follows:

- We designed a two-tiered ECC scheme to provide strong error protection for mixed 32B, 64B and 128B accesses in 3D HBM memory systems used in high performance GPUs. These three ECC schemes share the same core structure and can be configured statically and dynamically to support different sized accesses.

- Compared to a fixed 32B ECC scheme, Config-ECC increases the reliability by 200 times for both static and dynamic modes.

- Compared to a fixed 64B ECC scheme, Config-ECC increases the reliability by 20 times when the access size is 64B or larger. Also, Config-ECC can choose to

only read 32B of data to reduce the energy by 21% in the static mode and 17% in the dynamic mode.

This work has been submitted to MICRO 2017 [40].

### 1.4 Dissertation Organization

The rest of the dissertation is organized as follows.

In Chapter 2, basics of 2D and 3D DRAM architecture, error characteristics, existing ECC schemes for 2D and 3D DRAM and the machine check architecture (MCA) are introduced.

Chapter 3 focuses on ECC schemes for 2D DRAM systems. The data access pattern and decoding flowchart for all E-ECC schemes are presented. The tradeoff between system performance and reliability for each scheme is also analyzed.

Chapter 4 focuses on an ECC scheme, RATT-ECC, for an HBM system that services CPU requests. The operation of RATT-ECC is described in detail and the timing performance, reliability and implementation overhead are also analyzed.

Chapter 5 focuses on an ECC scheme, Config-ECC, for an HBM system that supports GPU data access sizes of 32B, 64B and 128B. Config-ECC design is described in detail along with the reliability and energy analysis.

Chapter 6 concludes the thesis.

## Chapter 2

## **BACKGROUND**

### 2.1 DRAM Memory Systems

## 2.1.1 2D Commodity DRAM Architecture

A DRAM memory system is organized into channels, ranks, chips and banks [41]. The DRAM memory controller (MC) acts as an interface between the last level cache and the DRAM. It can access data from one or more channels. Each channel consists of dual in-line memory modules (DIMMs), each of which consists of one or more ranks. A rank is the minimum unit that is activated in a read or write access. Each rank is composed of multiple chips (also called devices) and the number of chips to be activated depend on the size of the data bus width.

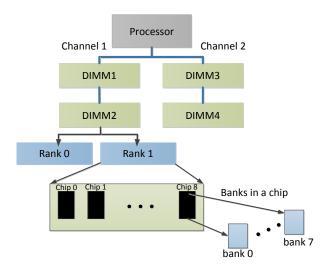

Figure 2.1: Logical View Of A DRAM Based Memory System

For DDR3, the I/O width (N) is typically 4, 8 or 16 bits. Since the 64 bit data path is fixed, a rank consists of 64/N chips. A DRAM system built with sixteen x4 DRAM chips is referred to as a 16x4 system. The common DRAM system configurations are 16 x4, 8 x8 and 4 x16 (number of chips per rank x data I/O width). In an x4 system, there are 8 extra ECC bits for every 64 bits data resulting in two extra ECC chips per rank. In an x8 system, one extra chip is used for ECC chip per rank. The DRAM architecture for a x8 system is shown in Figure 2.1.

In DDR3 systems, data is accessed in the burst mode; typically, burst length is eight or four (chopped burst) [42]. A burst length of eight means that eight beats of data are transferred per memory access [41]. Some DRAM systems operate in the lock-step mode [14,41]. In such a mode, two physical channels operate as a single logical channel. A single 64B cache line is fetched using two memory channels; one half of the cache line is accessed in the first channel while the second half is obtained from the second channel.

#### 2.1.2 3D DRAM Memory Architecture

There are several prototypes of 3D DRAM, for example, high bandwidth memory (HBM) [7,33], hybrid memory cube (HMC) [43] and Wide-I/O [44]. In this thesis, we consider a 3D DRAM architecture to be similar to HBM [7,33]. For each diestacked HBM, typically, there are eight dies to store data, where each die has eight or sixteen banks. A single stack is anticipated to support up to eight channels. Since each stack supports multiple channels, it provides larger bandwidth than 2D DRAM. Each channel accesses an independent set of DRAM banks. A data line is stored in the same bank in HBM in contrast to a data line being striped across multiple banks in conventional 2D DRAMs. Through-silicon-via (TSV) connects different data dies [45]. Each channel has data width of 128b as the most common setting in [7]; hence, there

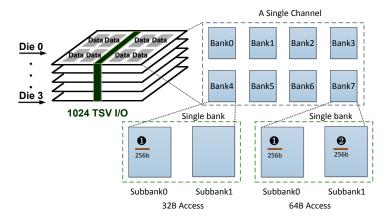

Figure 2.2: 32B vs. 64B Accesses in HBM2 (Pseudo Channel Mode)

are 128 TSV lines per channel. Since there are eight channels, there are a total of 1024 TSV lines per stack.

HBM has two different architectures: HBM1 and HBM2. The access unit is only 32B in HBM1 [7] while the access unit can be 32B or 64B in HBM2 [33]. Each bank in HBM2 consists of two sub-banks and these two sub-banks can be controlled by two sub-channels. The HBM2 architecture is shown in Figure 2.2. The I/O for each channel is 128b with additional 16b for ECC in [33,46], which is different from HBM1. Two modes are supported in HBM2: the legacy mode and the pseudo channel mode. In the legacy mode, in each request, 256b of data is read out from a single bank. Therefore, a 32B DRAM access consists of 2 bursts (1 cycle) with 128b accessed per burst through a single channel. Here, a burst means the rising edge or falling edge of a clock cycle.

To reduce activation power, the pseudo channel mode is proposed in the HBM2 standard <sup>1</sup>. In the pseudo channel mode, a single channel is divided into two subchannels each of size 64 bits. So a 32B access consists of 4 bursts (2 cycles) with 64b

<sup>&</sup>lt;sup>1</sup>HBM1 only supports the legacy mode while HBM2 supports both legacy and pseudo channel mode.

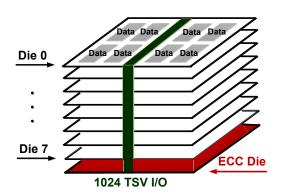

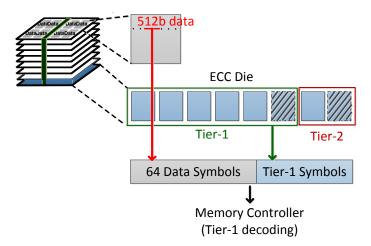

Figure 2.3: 3D HBM-Like Structure With An ECC Die

per access. HBM2 has separate pins for row and column commands and this dual command feature allows HBM2 to simultaneously issue row and column commands to two different banks. Thus, in a 64B access, two sub-channels are activated at the same time and the 64B access consists of 4 bursts (2 cycles).

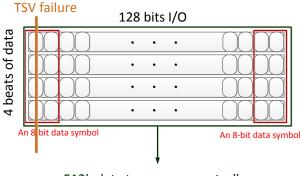

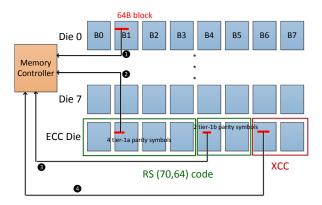

In Chapter 4, we assume an HBM structure that consists of 8 data dies and an additional ECC die to store the ECC bits as in [27]. Figure 2.3 shows the internal stack organization of such a memory. The parity check symbols for tier-1 and tier-2 code are stored in the ECC die. In each memory request, 512b of data is accessed from a certain bank of a single data die and the corresponding ECC bits are read from a certain bank in the ECC die. The data is read over four beats with 128 bits being read in each beat as shown in Figure 2.4. Eight data bits form a symbol and so a single TSV failure leads to only one symbol error as shown in Figure 2.4 as well.

In Chapter 5, we assume that the memory system that services GPUs uses the latest HBM2 standard [33] and develop ECC schemes for the pseudo channel mode. The ECC bits are stored in the data banks instead of being housed in another die as in [27]. In each access, the ECC bits are read along with the data bits. For 32B and

512b data to memory controller

Figure 2.4: 512b or 64 Symbols Are Read From A Bank In A Data Die

64B accesses, the burst length is 4 and considered as one request. For 128 access, we assume that the system issues two 64B requests.

#### 2.2 DRAM Error Characteristics

## 2.2.1 2D Commodity DRAM Errors

DRAM errors can be broadly classified into soft errors and hard errors. Soft errors are caused by transient faults which occur randomly and cause incorrect data to be read from a memory location; they disappear when the location is overwritten. Hard errors are caused by permanent faults or intermittent faults. A permanent fault causes a memory location to consistently return an incorrect value, such as a stuck-at-0 fault. An intermittent fault causes a memory location to sometimes return incorrect values. Note that a single fault can result in multiple error instances [3, 4].

DRAM faults consist of single-bit, single-word, single column, single row, single-bank, multiple-bank and multiple-rank failures [3]. We use the definition from [3] and present the terminology here:

#### 1. **Single-bit:** All errors map to a single bit.

Table 2.1: DRAM Fault Modes in Hopper

| Fault Mode    | Total Faults | Transient | Permanent |

|---------------|--------------|-----------|-----------|

| Single-bit    | 78.9%        | 42.1%     | 36.8%     |

| Single-column | 5.9%         | 0.0%      | 5.9%      |

| Single-row    | 9.2%         | 1.8%      | 7.4%      |

| Single-bank   | 4.3%         | 0.4%      | 3.9%      |

| Multiple-bank | 0.6%         | 0.0%      | 0.6%      |

| Multiple-rank | 1.0%         | 0.2%      | 0.8%      |

| Summary       | 99.9%        | 44.5%     | 55.4%     |

2. **Single-word:** All errors map to a single word.

3. Single-column: All errors map to a single column.

4. **Single-row:** All errors map to a single row.

5. **Single-bank:** All errors map to a single bank.

6. Multiple-bank: Errors map to multiple banks.

7. **Multiple-rank:** Errors map to multiple DRAMs in the same lane.

Table 2.1 shows a breakdown of DRAM faults from [26].

DRAM errors have been analyzed in detail in [2–4,25,47]. The study in [2,3,25] shows that a large fraction of errors are hard errors and these manifest as repeating errors occurring at the same address, row, column or chip. In addition, permanent faults tend to be clustered [25]; these errors have strong correlations in space and time. The repeated errors contaminate the nearby rows and columns and increase dramatically in the presence of prior errors. The study in [2,25] also shows that the

number of errors in any memory system increase over time. A more recent analysis of DRAM faults performed over a period of 15 months shows that while the failure rate due to transient faults increases mildly, the failure rate due to permanent faults is higher in the beginning and becomes almost the same as transient faults around months six to eight [4]. It is projected that the failure rate would again increase towards the end of the device's lifetime.

In general, if a chip has persistent errors, then that chip can be marked as faulty and all data from that chip can be treated as erasures. Note that erasures are defined as errors whose locations are known [5]. Thus if erasures can be corrected, the faulty chip can continue to be used instead of being retired. In this work, we utilize the error recording mechanism of machine-check architecture (MCA) [20, 21] to mark a chip as faulty.

### 2.2.2 3D Die-Stacked DRAM Errors

For 3D DRAM errors, a better classification is based on the granularity of faults. Small granularity faults are those due to single bit or single column and account for 70% of all faults, and large granularity faults are due to row and bank failures [3,4,26]. 3D DRAM also has errors due to TSV failures [27,28], which fall under small granularity faults. In this work, we analyze the capability of the system to handle errors due to small granularity and large granularity faults (transient and permanent). To handle permanent faults such as TSV faults (small granularity) and bank faults (large granularity), we also utilize the error recoding mechanism of MCA [21].

## 2.3 Existing ECC Mechanisms

## 2.3.1 Existing Schemes in 2D DRAM

Chipkill-Correct is the most common error protection scheme for DRAM memory systems [2,10,11,48]. It can correct errors due to failure of one chip and also detect errors due to two chip failures. The original Chipkill-Correct solution from IBM [10] used single bit error correction and double bit error detection code (SEC-DED). Current systems such as Sun UltraSPARC-T1/T2 [49] and AMD Opteron [50] systems use symbol based Chipkill-Correct codes. An example of such a code is the rotational (144,128) code [12], which is a (36,32) code over GF(2<sup>4</sup>). In an x4 memory system, this code results in activation of 36 devices across 2 ranks and thus consumes a lot of power. Next we describe several methods that try to achieve a balance between reduction in power consumption and Chipkill-Correct reliability.

Virtualized ECC (V-ECC) [14] provides Chipkill-Correct capability for x4 and x8 DRAM systems. It is based on a 3 check symbol code where 2 check symbols are used for detection (tier-1) and a third check symbol is used for correction (tier-2). In an x8 system, V-ECC activates 18 chips in 2 ranks. It caches the tier-2 symbols to reduce the read latency and write frequency. However, it still incurs extra read/write operations to perform error correction or to update the ECC bits. The storage overhead of V-ECC is 18.75%.

Localized and tiered ECC (LOT-ECC) [15] activates only nine chips per rank in x8 DRAM systems to reduce power consumption. It uses multiple layers of XOR operations to deal with memory errors. Data along with local and global ECC parity bits are stored in the same DRAM row to improve access efficiency. If errors are detected, global parity bits are read by a second access. LOT-ECC is not a Chipkill-Correct solution since it can only correct a stuck-at-0 or stuck-at-1 chip

failure. The storage overhead of LOT-ECC is 26.5%, which is higher than the existing schemes.

Multi-line error correction (Multi-ECC) [16] also activates only nine chips per rank in x8 DRAM systems. Multi-ECC uses a different approach where errors are first detected along rows and then column checksums are used to locate the errors. The row parity bits are then used to correct these errors. This method requires a large number of data reads when an error is detected. In addition, since Multi-ECC uses one's complement for column checksums, it cannot fully detect errors due to column failures. The storage overhead of this method is only 12.9%, which is a small increase compared to Chipkill-Correct.

Adaptive Reliability Chipkill Correct (ARCC) [51] also provides two tiers of error protection. It reduces the power consumption by activating only one rank when there are no errors. When errors are detected, ARCC adaptively adjusts the ECC strength by combining adjacent codewords to perform error correction. Once two ranks are combined, the cache line size is increased from 64B to 128B. ARCC does not increase the ECC storage overhead; the only overhead is that the last level cache needs to be modified to accommodate both 64B and 128B cache lines.

Bamboo-ECC [52] is a recently proposed single-tier error protection scheme that provides good system reliability with low storage overhead. It uses an 8-bit symbol based RS code for x4 DRAM systems to handle error events ranging from correcting single bit errors with 3.1% storage overhead to correcting errors due to two chip failures with 25% storage overhead. Furthermore, by grouping per-pin data to form ECC symbols, it is able to correct double pin failures and thus provides higher error protection compared to Chipkill-Correct.

### 2.3.2 Existing Schemes In 3D DRAM

We give a brief description of prior approaches on improving the reliability of 3D Die-stacked DRAM [27–30]. Of these schemes, Efficient-RAS [28] and Citadel [27] also focus on an HBM-like structure and are closest to our proposed scheme.

Subarraykill [29] corrects errors due to a subarray failure in Tezzaron Octopus structure. A cache line is striped across a subset of subarrays; the number of subsets depends on the page size. Due to this striped pattern of data storage, the ECC schemes based on symbol-based code can be used.

Resilient-DRAM-Caches [30] uses ECC codes to protect tags and cache lines in 3D DRAM caches. Single bit error correction (SEC) code is used to correct single bit errors while cyclic redundancy check codes (CRCs) are used to detect multiple bit errors. To recover multiple bit errors due to row or bank failures in a contaminated cache line, a duplicate dirty cache line that is stored in another DRAM cache bank is utilized. This approach has high storage overhead and is not strong enough to handle errors in 3D DRAM.

Efficient-RAS [28] proposes a two tier error correction scheme with higher than 12.5% storage overhead. The first tier uses a symbol-based ECC code to correct errors due to small granularity faults, while the second tier is a XOR-based correction code (XCC) to correct the detectable but uncorrectable errors due to large granularity faults. It proposes a strategy to deal with permanent TSV (or row) failures by using spare TSVs (or rows). However, it does not have any strategy to handle permanent bank failures.

Citadel [27] also uses a two tier ECC protection to handle small and large granularity faults. For the first tier, Citadel uses CRC-32 to provide strong error detection capability. After errors are detected, Citadel relies on multiple levels of parity (3DP)

to recover from errors due to single bit, single column, single TSV faults as well as row and bank failures. In this scheme, the cost of correcting errors is very high. Citadel allocates 64 bits for each cache line; the metadata is located in ECC logic die resulting in a 12.5% additional storage. Additional bits are used to address TSV failures and for data recovery by 3DP. In addition, it provides for two spare banks to handle bank failures.

Parity-Helix [31] focuses on design of the tier-2 code and allows the system to recover from errors due to a single channel failure or a single die failure in a diestacked DRAM. The ECC core structure is based on RAID-5. The ECC parity blocks in vertical and horizontal directions are twisted to form a helix structure which can avoid a single dimensional fault in a multi-dimensional memory system. The storage overhead is 26.8% for the overall ECC scheme with 14.3% for the tier-2 code.

# 2.4 Error Logging Architecture

The memory controller not only manages the data access from and to DRAM but also performs error detection and correction. Many server systems utilize machine-check architecture (MCA) [3, 21, 53, 54] to record detected errors in each machine. MCA defines the facilities by which processor and system hardware errors are logged and reported to the system software (operation system) [21]. These detected errors include corrected and uncorrected error events but the MCA does not record the errors due to miss error detection. Once errors are detected, the CPU sends a hardware exception signal called a machine check exception (MCE) which must be handled by the processor.

When an MCE event occurs, the memory controller logs corrected error events in registers provided by the MCA [3,21]. Each machine's operating system is configured to poll the MCA registers once in a certain period (e.g., few seconds) and record

any exception event. These console logs contain a variety of information about the physical address associated with the error, the time that the error was corrected, the type of memory access (e.g., read or write), the type of error (corrected or uncorrected) and the ECC syndrome associated with the error.

For 2D DRAM memory systems, if the number of errors is larger than a threshold value (the threshold value is system-dependent), the chip is marked as faulty by the memory controller. The erasure correction scheme is launched and the corresponding ECC mechanisms are discussed in Chapter 3.

For 3D DRAM memory systems, if the number of errors is larger than a threshold value (the threshold value is system-dependent), the specific TSV line or bank can be marked as faulty by the memory controller. If a TSV is marked as faulty, we utilize the erasure correction capability of the tier-1 code and if the data banks are marked as faulty, we reduce the parity storage of the tier-1 and tier-2 codes to free up banks in the ECC die as discussed in Chapter 4.

## Chapter 3

### 2D DRAM ECC SCHEMES

In this chapter we describe our work on designing reliable ECC schemes that provide at least Chipkill-Correct capability for different commodity DRAM systems, namely, x4, x8 and x16 systems. The goal is to balance the tradeoffs between performance, reliability, storage overhead and power consumption by designing ECC schemes tailored to the characteristics of the different DRAM systems.

Our solution is to use erasure and error correction code (E-ECC) to deal with random errors as well as errors due to chip failures. We make use of erasure codes to correct the errors due to a chip that has already been marked as faulty by MC. This helps in increasing the lifetime of the device. We believe that this is a more cost-effective way of increasing the lifetime compared to systems that use chip sparing or bit steering. Furthermore, our proposed schemes do not incur extra read or write operations to perform ECC correction or to update ECC bits.

We describe the proposed E-ECC schemes for x4 DRAM systems in Section 3.1, for x8 DRAM systems in Section 3.2 and for x16 DRAM systems in Section 3.3. For each scheme, we describe the data access pattern and the decoding flowchart. The actual decoding algorithms and the corresponding synthesis results are included in the Appendix A and Section 3.4, respectively. We also analyze the tradeoff between the reliability and system performance (timing, power and energy efficiency) for our proposed schemes and the existing schemes in Section 3.5.

## 3.1 Proposed E-ECC Schemes For x4 DRAM Systems

For x4 DRAM systems, we present three schemes that all have 12.5% storage overhead but differ in the number of ranks being activated. E-ECC Schemes 1 and 2 operate in lockstep mode while E-ECC Scheme 3 only activates one rank per access. The specific ECC codes used in these three schemes are rotational (144,128) code over  $GF(2^4)$  and RS (36,32) code over  $GF(2^8)$ . The schemes that activate two ranks per memory access have lower timing, power and energy performance but higher reliability compared to the one that activates only one rank.

### 3.1.1 E-ECC Scheme 1 - x4 DRAM System

Chipkill-Correct uses 4-check symbol codes to correct errors due to a single chip failure and detect errors due to two chip failures. We use rotational (144,128) code [12] as the representative Chipkill-Correct code in this work. Here, 36 devices are activated across two ranks in each access. Each device provides four bits of data per beat, that is, 36x4 = 144 bits per beat, to the ECC decoding unit. Each set of 144 bits is decoded to obtain 128 data bits and a total of 4x128 = 512 data bits is sent to the last level cache.

The rotational (144,128) code has a minimum distance of 4 and so this code can support the following cases: (i) single symbol correction and double symbol detection, (ii) single erasure correction, (iii) single erasure and single error correction, (iv) double erasure correction and (v) double erasure and single error detection. Current Chipkill-Correct x4 systems implement only single symbol correction and double symbol detection (case (i)). Here, we propose an enhancement which makes use of the same (144,128) code to handle erasures; we refer to it as **E-ECC Scheme 1**.

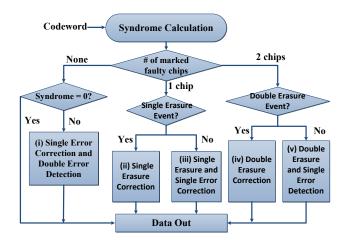

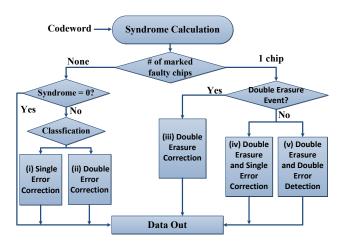

Figure 3.1: Overview Of The Decoding Algorithm For E-ECC Scheme 1

If a chip is marked as faulty, it leads to a single erasure and Scheme 1 performs single erasure correction (case (ii)). When one more random error occurs in another chip, Scheme 1 can still correct it (case (iii)). The decoder first checks if it is a single erasure event. If so, case (ii) is executed; otherwise, case (iii) is activated. If a second chip fails, the MC marks it as faulty. The decoder first checks if it is a double erasure event. If so, double erasure correction (case (iv)) is implemented; otherwise, double erasure and single error detection (case (v)) is activated. The decoding flowchart for Scheme 1 is shown in Figure 3.1 and the details of the decoding algorithm are included in Appendix A.

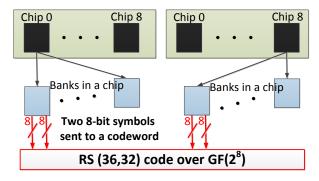

## 3.1.2 E-ECC Scheme 2 - x4 DRAM System

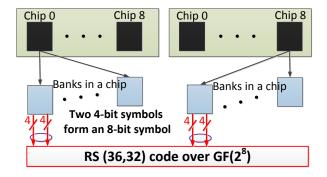

To enhance the error correction capability of x4 DRAM systems, we investigate ECC codes operating in higher finite field. We combine data from two beats to obtain 256 data bits and 32 ECC bits. Since there is no RS (72,64) code over  $GF(2^4)$ , we move to  $GF(2^8)$ . We propose using RS (36,32) in  $GF(2^8)$ , which can be derived from RS (255,251). RS (36,32) can provide double error correction, that is, it can correct

double chip failures on the fly instead of only detecting them as in Scheme 1. We refer to this method as **E-ECC Scheme 2**.

In Scheme 2, two ranks (with 18 chips per rank) are activated per access. In each read/write, two consecutive 4-bit symbols from the same bank form a single 8-bit symbol, and thus a total of 36 symbols are read out. Figure 3.2 illustrates the data access pattern. The proposed RS (36,32) E-ECC code has a minimum distance of 5 and supports the following cases: (i) single error correction, (ii) double error correction, (iii) single erasure correction, (iv) single erasure and single error correction.

Figure 3.2: E-ECC Scheme 2. x4 DRAM Access Pattern Of Two Ranks.

Figure 3.3: E-ECC Scheme 2. Overview Of The Decoding Algorithm.

The default state of Scheme 2 is single error and double error correction. Since RS code has a special algebraic structure, the decoder can use the syndrome to distinguish between case (i) and case (ii) efficiently [55]. When a chip fails, it leads to a single error in the E-ECC codeword and a single error can be corrected easily. When MC marks this chip as faulty, the error becomes an erasure in an ECC codeword and the decoding circuitry for single erasure correction (case (iii)) is activated. Correcting single erasure is simpler compared to correcting single error (see Appendix A). Furthermore, if there is an additional error in another chip, it can be corrected as well (case (iv)). We assume that the errors build up over time and so a second faulty chip can start generating repeated errors. When MC marks the second chip as faulty, the E-ECC decoder activates double erasure correction (case (v)). Once two chips are marked as faulty, it can correct one more random error (case (vi)). The decoding flowchart is shown in Figure 3.3 and details of the decoding algorithm for each case is given in Appendix A.

## 3.1.3 E-ECC Scheme 3 - x4 DRAM System

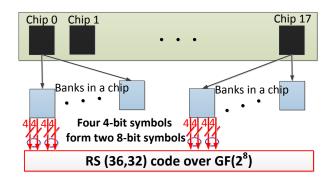

Although Scheme 2 improves the reliability compared to Chipkill-Correct and E-ECC Scheme 1, it still activates 36 devices and consumes significant amount of power. This motivates us to find another scheme that activates fewer chips at the cost of some loss in reliability. We investigate codes in  $GF(2^4)$  and  $GF(2^8)$  with the constraint that 18 chips can be activated in each access. Under this constraint, in each beat, 72 bits (64 data bits + 8 ECC bits) are accessed from 18 chips. Since there is no RS (18,16) code over  $GF(2^4)$ , we move to  $GF(2^8)$ .

In  $GF(2^8)$ , the only available code is RS (9,8), which has a minimum distance of 2 and so cannot even correct one single error. However, if we combine data from two beats (144 bits), there are two candidates: one is the rotational (144,128) code

and the other is the RS (18,16) code over  $GF(2^8)$ . Rotational code cannot correct one chip failure (there are 2 x4 symbol errors due to a chip failure) and hence it is not suitable. The RS (18,16) code has minimum distance of 3 and can perform single error correction. It seems to be used in AMD Chipkill-Correct [52]. Although this code provides Chipkill-Correct capability, we choose a stronger code whose error correction capability is competitive with the other proposed schemes. Specifically, we choose RS (36,32) code over  $GF(2^8)$ ; the corresponding scheme is referred to as Scheme 3.

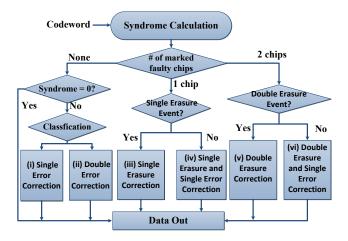

In Scheme 3, four consecutive 4-bit symbols from the same bank contribute towards a codeword. Figure 3.4 describes the corresponding data access pattern. As mentioned earlier, the RS (36,32) code has a minimum distance of 5 and supports the following cases: (i) single error correction, (ii) double error correction, (iii) double erasure correction, (iv) double erasure and single error correction (v) double erasure and double error detection.

The default state of Scheme 3 is also single error and double error correction. When a chip fails, it leads to two errors in the E-ECC codeword and these two errors can be corrected on the fly. When MC marks a chip as faulty, the decoding circuitry for double erasure correction (case (iii)) is activated. The double erasure correction methods for Schemes 2 and 3 are different. In Scheme 2, two chip failures lead to two erasure symbols in a codeword, which may not be adjacent. In Scheme 3, one chip failure leads to double erasures and these two erasure symbols are adjacent in a codeword.

Correcting two erasures is simpler compared to correcting two errors (see Appendix A) and these two erasure addresses are consecutive in Scheme 3. Furthermore, if there is an additional error in another chip, it can be corrected as well (case (iv)). If a second chip fails, there are two erasures (from the chip marked faulty) and two errors (from

the other faulty chip) which can be detected but not corrected (case (v)). Note that the system cannot use case (iv) and case (v) at the same time and a choice has to be made. For DRAM systems whose errors increase over time, the MC can activate case (iv) decoder, and once the number of single errors is larger than a threshold, it can activate the circuitry for case (v). The decoding flowchart is shown in Figure 3.5 and details of the decoding algorithm for each case is given in the Appendix A.

Figure 3.4: E-ECC Scheme 3. x4 DRAM Access Pattern Of One Rank

Figure 3.5: E-ECC Scheme 3. Overview Of The Decoding Algorithm

Figure 3.6: E-ECC Scheme 4. x8 DRAM Access Pattern

3.2 Proposed E-ECC Schemes For x8 DRAM Systems

## 3.2.1 E-ECC Scheme 4 - x8 DRAM System

In an x8 DRAM system, nine chips (8 data chips + 1 ECC chip) are accessed every time and since fewer chips are activated compared to x4 DRAM, the power consumption is lower. Hence, a lot of research effort has focused on designing Chipkill-Correct x8 DRAM systems [14–16, 51, 56].

Deriving a Chipkill-Correct solution for x8 DRAM with low overhead is still quite a challenge. If only one rank is activated, in each beat, nine symbols are accessed from nine chips. A possible choice is the RS (9,8) code over  $GF(2^8)$ . Unfortunately, this code can only detect a single symbol error and thus is not suitable. If two beats of data are combined, RS (18,16) code can be used over  $GF(2^8)$  to perform single error correction. However, since one faulty chip leads to two error symbols per codeword, this code can not correct them. To provide Chipkill-Correct protection, either an extra ECC chip (3-check symbol code) has to be used or the extra ECC symbols have to be stored in another rank like [14].

Our solution is to operate the x8 DRAM system in lock-step mode as in Intel [19], HP [57] and Dell [58] systems. In the lock-step mode, two ranks are activated and in each beat, 144 bits (128 data bits + 16 ECC bits) are accessed from 18 chips

across two ranks. If we use the rotational (144,128) code, when a chip fails, the faulty chip leads to 2 x4 error symbols in a codeword and since this code cannot correct two random errors, it is not Chipkill-Correct. In GF(2<sup>8</sup>), the RS (18,16) code is a possible choice. It can correct errors due to a chip failure. When MC marks a chip as faulty, it can correct single erasure and detect one more random error in another chip. However, we choose a stronger code, namely, RS (36,32), since it has better error correction capability compared to RS (18,16) and the same 12.5% storage overhead. We refer to this scheme as **E-ECC Scheme 4**.

In each beat, 2x9 = 18 symbols are read out from two ranks and a total of 2x18 = 36 symbols are accessed in two beats. Figure 3.6 demonstrates the data access pattern of Scheme 4. As mentioned earlier, the RS (36,32) code supports: (i) single error correction, (ii) double error correction, (iii) double erasure correction, (iv) double erasure and single error correction (v) double erasure and double error detection. Scheme 4 uses the same RS (36,32) code as Scheme 3, though their access patterns are different (Scheme 4 is designed for x8 DRAM systems while Scheme 3 is for x4 DRAM systems). The decoding flow of Scheme 4 is the same as Scheme 3 (shown in Figure 3.5). When none of the chips are marked as faulty, Scheme 4 performs cases (i) and (ii). When a chip is marked as faulty, both symbols from that chip are treated as erasures. The decoder checks whether it is a double erasure event. If so, it launches double erasure correction (case (iii)); otherwise, it activates double erasure and single error correction (case (iv)) or double erasure and double error detection (case (v)). Note that case (iv) and case (v) cannot be chosen at the same time.

Figure 3.7: E-ECC Scheme 5. x16 DRAM Access Pattern

3.3 Proposed E-ECC Schemes For x16 DRAM Systems

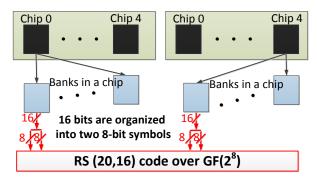

## 3.3.1 E-ECC Scheme 5 - x16 DRAM System

x16 DRAM activates fewer number of chips per rank compared to x4 and x8 DRAM systems and thus has even lower power. Since each rank has four chips for data, there has to be at least one additional chip per rank to provide Chipkill-Correct reliability. Thus, such a scheme results in a storage overhead of 25%. If only one rank is activated, five 16-bit symbols are read out in each beat. This can be configured into ten 8-bit symbols and the RS (10,8) code over  $GF(2^8)$  can be used. While the RS (10,8) code can correct a single symbol error, it cannot correct double errors due to a faulty chip. The RS (5,4) code over  $GF(2^{16})$ , on the other hand, can detect a faulty chip but cannot correct the errors due to that faulty chip. If two beats of data are combined, the RS (20,16) code over  $GF(2^8)$  or the RS (10,8) code over  $GF(2^{16})$  can be used. Unfortunately, both these codes cannot correct errors due to a faulty chip. Hence, we move to x16 DRAM systems that operate in the lock-step mode.

When two ranks are activated, in each beat, 160 bits (128 data bits + 32 ECC bits) are accessed. If RS (20,16) code over  $GF(2^8)$  is used, double errors due to a single faulty chip can be corrected. Although RS (10,8) code over  $GF(2^{16})$  is also a Chipkill-Correct code, RS (20,16) over  $GF(2^8)$  provides stronger and more flexible

error correction capability with the same 25% storage overhead. It can correct two random symbol errors in two different chips and also can correct two symbol errors in a single chip. Hence, we choose RS (20,16) code over GF( $2^8$ ) as our **E-ECC Scheme** 5.

Figure 3.7 illustrates the data access pattern. Here two ranks with five chips per rank are activated each time. The 16 bits per chip are organized into two 8-bit symbols in a codeword. The proposed RS (20,16) code also has a minimum distance of 5 and supports the following cases: (i) single error correction, (ii) double error correction, (iii) double erasure correction, (iv) double erasure and single error correction (v) double erasure and double error detection. Scheme 5 has the same decoding flow as Schemes 3 and 4 (also shown in Figure 3.5), though its access pattern is quite different. As before, when none of the chips are marked as faulty, Scheme 5 performs cases (i) and (ii). When a chip is marked as faulty, one 16-bit symbol failure from that chip is treated as two 8-bit erasures. The decoder checks whether it is a double erasure event. If so, Scheme 5 launches double erasure correction (case (iii)); otherwise, it activates double erasure and single error correction (case (iv)) or double erasure and double error detection (case (v)). Note that case (iv) and case (v) cannot be used at the same time.

### 3.4 Synthesis Results

We implemented the E-ECC decoders in Verilog hardware description language and synthesized them with a 28nm industrial process. The synthesis was done in collaboration with Supreet Jeloka of University of Michigan. Recall that Scheme 1 is based on the rotational (144,128) code, Schemes 2, 3, 4 are based on the RS (36,32) code over GF(2<sup>8</sup>), and Scheme 5 is based on the RS (20,16) code over GF(2<sup>8</sup>). The

latency, power consumption and area of each block in the three E-ECC codes are presented in Tables 3.1, 3.2 and 3.3, respectively.

The two main hardware components are finite field multiplication and finite field inversion. We used a fully parallel implementation for finite field multiplication. We implemented finite field inversion using a look-up table of size  $16 \times 4$  for  $GF(2^4)$  and  $256 \times 8$  for  $GF(2^8)$ . The syndrome calculation unit is activated in every read operation and so it is important that its latency be minimized. We implemented this unit using  $144 \ GF(2^4)$ ,  $144 \ GF(2^8)$  and  $80 \ GF(2^8)$  multiplications for rotational (144,128) code, RS(36,32) code and RS(20,16) code, respectively, followed by a tree of XOR gates.

Latency: The syndrome calculation unit of Scheme 1 (based on the (144,128) code) has a latency of 0.41ns. If the syndrome vector is not zero and the error event is single error, correcting the errors takes an additional 0.41ns. This low latency comes at the cost of additional area due to parallelization. If a chip is marked as faulty, single erasure correction takes 0.3ns. In addition to the erasures, if there is one more random error, it takes another 1.1ns. If two chips are marked as faulty, Scheme 1 takes 0.39ns to do double erasure correction. If there is one more random error, Scheme 1 can detect this error but can not correct it, and the corresponding timing delay is also 0.39ns.

The syndrome calculation unit of Scheme 2 (based on RS (36,32) code) takes 0.48ns. If the syndrome vector is not zero, RS (36,32) can classify whether it is a single error event or a double error event. Single error correction takes an additional 0.47ns, making the total latency 0.95ns. Double error correction takes an additional 1.07ns, making the total latency 1.55ns. When a chip is marked as faulty, Scheme 2 checks whether it is a single erasure event. If so, it implements single erasure correction with an additional 0.33ns; otherwise, it implements single erasure and single error correction with an additional 0.33+0.68ns. In Schemes 3 and 4, when a chip is

Table 3.1: Synthesis Results Using A 28nm Library - Latency

|                               | Rotational (144,128)                       | Shortened RS (36,32)                        | Shortened RS (20,16)                    |  |

|-------------------------------|--------------------------------------------|---------------------------------------------|-----------------------------------------|--|

|                               | Code over $GF(2^4)$                        | Code over $GF(2^8)$                         | Code over $GF(2^8)$                     |  |

| Syndrome Calculation          | $0.41 \mathrm{ns} \; (\Delta)$             | $0.48 \mathrm{ns} \; (\Lambda)$             | $0.42\mathrm{ns}(\nu)$                  |  |

| Corrects 1 error              | $\Delta + 0.41 \mathrm{ns}$                | $\Lambda + 0.47 \mathrm{ns}$                | $\nu + 0.47 { m ns}$                    |  |

| Corrects 1 erasure            | $\Delta + 0.30 \mathrm{ns}$                | $\Lambda + 0.33 \mathrm{ns}$                | N/A                                     |  |

| Corrects 1 erasure & 1 error  | $\Delta + 0.30 \text{ns} + 1.1 \text{ ns}$ | $\Lambda + 0.33 \text{ns} + 0.68 \text{ns}$ | N/A                                     |  |

| Corrects 2 errors             | N/A                                        | $\Lambda + 1.07 \mathrm{ns}$                | $\nu + 1.07 \text{ns}$                  |  |

| Corrects 2 erasures           | $\Delta + 0.39 \mathrm{ns}$                | $\Lambda + 0.78 \mathrm{ns}$                | $\nu + 0.79 \text{ns}$                  |  |

| Corrects 2 erasures & 1 error | N/ A                                       | $\Lambda + 0.78 \text{ns} + 0.87 \text{ns}$ | $\nu + 0.79 \text{ns} + 0.86 \text{ns}$ |  |

marked as faulty, E-ECC decoder checks for double erasures. If so, it implements double erasure correction with an additional 0.78ns; otherwise, it implements double erasure and single error correction with an additional 0.78+0.87ns.

The syndrome calculation unit in Scheme 5 takes only 0.42ns because Scheme 5 is based on a smaller RS code. When none of the chips are marked faulty, Scheme 5 performs single error correction with an additional 0.47ns and double error correction with an additional 1.07ns. When a chip is marked as faulty, double erasure correction takes an additional 0.79ns. If there is one more random error, it performs double erasure and single error correction with an additional 0.79+0.86ns.