# Implementation of Pilot Protection System for Large Scale Distribution System like The Future Renewable Electric Energy Distribution Management Project

By

Varun Iyengar

A Thesis Presented in Partial Fulfillment Of the Requirements for the Degree Master of Science

Approved April 2014 by the Graduate Supervisory Committee:

George Karady, Chair Raja Ayyanar Keith Holbert

ARIZONA STATE UNIVERSITY

May 2014

#### **ABSTRACT**

A robust, fast and accurate protection system based on pilot protection concept was developed previously and a few alterations in that algorithm were made to make it faster and more reliable and then was applied to smart distribution grids to verify the results for it. The new 10 sample window method was adapted into the pilot protection program and its performance for the test bed system operation was tabulated. Following that the system comparison between the hardware results for the same algorithm and the simulation results were compared. The development of the dual slope percentage differential method, its comparison with the 10 sample average window pilot protection system and the effects of CT saturation on the pilot protection system are also shown in this thesis. The implementation of the 10 sample average window pilot protection system is done to multiple distribution grids like Green Hub v4.3, IEEE 34, LSSS loop and modified LSSS loop. Case studies of these multi-terminal model are presented, and the results are also shown in this thesis. The result obtained shows that the new algorithm for the previously proposed protection system successfully identifies fault on the test bed and the results for both hardware and software simulations match and the response time is approximately less than quarter of a cycle which is fast as compared to the present commercial protection system and satisfies the FREEDM system requirement.

#### **ACKNOWLEDGMENTS**

I would like to express my heartfelt gratitude to my research advisor and mentor Dr. George G. Karady for advising on my research as well as continuing support. His rigorous, meticulous and expertise, have been influential in performing this research work, and also been a great inspiration throughout my entire Master tenure. I would also like to thank my supervisory committee members, Prof. Raja Ayannar and Prof. Keith Holbert for their valuable suggestions and for being on the supervisory committee. I am obliged to the entire faculty of the power systems group at Arizona State University for their guidance inside and outside the classroom.

I am also very grateful to NSF and FREEDM project for providing me this great opportunity to perform research work. I would thank Mayur Kulkarmi, Andrew Rogers, Pavan Chandra, their generous help towards this research. I would also like to thank Dr. Mesut Baran and Urvir Singh from NCSU, Dr Mariesa Crow and Darshit Shah at MS&T and Dr. Mischa Steurer, Chris Widener and Passinam Tatcho at FSU.

My sincere thanks also goes to my lab mates and all members in our research group for always supporting me. I would like to thank my parents deeply for their support and encouragement during the hard moments. Without you, this couldn't be possible.

# TABLE OF CONTENTS

|                |                                                          | Page |

|----------------|----------------------------------------------------------|------|

| LIST OF TABLE  | S                                                        | viii |

| LIST OF FIGURI | ES                                                       | x    |

| LIST OF SYMBO  | OLS / NOMENCLATURE                                       | xvi  |

| CHAPTER        |                                                          |      |

| 1 INTROD       | UCTION                                                   | 1    |

|                | 1.1 Brief Introduction                                   | 1    |

|                | 1.2 The Freedm System                                    | 3    |

|                | 13 Motivation And Objective                              | 6    |

|                | 1.4 Thesis Outline                                       | 8    |

| 2 LITERAT      | ΓURE REVIEW                                              | 11   |

|                | 2.1 Solid State Transformer                              | 11   |

|                | 2.1.1 SST Design                                         | 11   |

|                | 2.1.2 SST Converter Stages And Its Simulation Parameters | 11   |

|                | 2.1.3 Rectifier Modelling                                | 13   |

|                | 2.1.4 Modelling Of The Inverter Stage                    | 17   |

|                | 2.2 Relay Protection Design                              | 17   |

|                | 2.3 Design Criteria For Protection Applications          | 18   |

|                | 2.4 Zones Of Protection                                  | 19   |

|                | 2.5 Different Types Of Protection Schemes Used           | 20   |

|                | 2.5.1 Overcurrent Protection                             | 20   |

| CF | HAPTER Page                                                           |

|----|-----------------------------------------------------------------------|

|    | 2.5.2 Differential Relays                                             |

|    | 2.5.3 Principle Of Current Differential Relay22                       |

|    | 2.5.4 Percentage Differential Relay24                                 |

|    | 2.5.5 Pilot Protection                                                |

|    | 2.5.6 Directional Overcurrent Protection                              |

|    | 2.6 Use Of Pilot Line Differential Protection: A Comparative Study28  |

| 3  | UPDATED ALGORITHM AND THE COMPARISON OF THE HARDWARE TEST             |

|    | AND SIMULATION RESULTS                                                |

|    | 3.1 Intelligent Fault Management System Theory32                      |

|    | 3.2 Protection Zone Concept                                           |

|    | 3.3 Sampling Data38                                                   |

|    | 3.4 Explanation Of Current Differential Algorithm39                   |

|    | 3.5 Traditional Over Current Protection Using The SEL-351 S Relay43   |

|    | 3.6 SEL 351 S Relay46                                                 |

|    | 3.7 New Pilot Protection Algorithm And Its Simulation On The Test Bed |

|    | 49                                                                    |

|    | 3.8 Pilot Protection Model Simulation Is PSCAD51                      |

|    | 3.8.1 Construction And Testing Of Backup Overcurrent                  |

|    | Protection Component53                                                |

|    | 3.8.2 Investigation Of Hardware Communication And Processing          |

|    | Delav54                                                               |

| CHAPTER Page                                                       |

|--------------------------------------------------------------------|

| 3.8.3 Rolling Window Concept60                                     |

| 3.8.4 Investigation Of Fault Timing On Pilot Protection Algorithm  |

| Reliability And Consistency For The Test Bed Simulation In Pscad61 |

| 3.9 Hardware Test Setup And Comparison With Pscad Simulations65    |

| 3.9.1 System Hardware And Description65                            |

| 3.9.2 System Functioning65                                         |

| 3.9.3 Scan Mode                                                    |

| 3.9.4 Fpga Mode69                                                  |

| 3.9.5 Timer And Counter69                                          |

| 3.9.6 Protection Algorithm:70                                      |

| 3.9.7 Over Current Protection:70                                   |

| 3.9.8 Timed Loop:70                                                |

| 3.9.9 Averaging Window Concept Implementation On The Ni Crio:      |

| 71                                                                 |

| 3.9.10 Need For Rolling Window In The Real Time Simulation71       |

| 3.10 Results                                                       |

| 3.11 Scan Mode                                                     |

| 3.12 Comparative Study Of The Two Algorithms76                     |

| 3.13 Fpga Mode77                                                   |

| 3.14 Conclusion                                                    |

| 4 MULTI SLOPE DIFFERENTIAL PROTECTION AND CT SATURATION EFFECT     |

| ON THE PILOT PROTECTION SYSTEM 80                                  |

| 4.1 Multi Slope Differential Protection Or Point Form Differentia     |

|-----------------------------------------------------------------------|

| Protection80                                                          |

| 4.2 Results For Dual Slope Method86                                   |

| 4.3 Results For The Same Test Using The Percentage Differential Slope |

| With 10 Sample Rolling Window88                                       |

| 4.4 CT Saturation Phenomenon And The Performance Of The Percentage    |

| Slope Differential Protection With 10 Sample Window Average Module 89 |

| 4.4.1 Saturation Of CT Due To DC Offset90                             |

| 4.4.2 Explanation Of The CT Saturation92                              |

| 4.4.3 Test Results Of CT Saturation On PSCAD93                        |

| 5 IMPLEMENTATION OF THE PILOT PROTECTION SYSTEM FOR LARGE             |

| DISTRIBUTION SYSTEMS                                                  |

| 5.1 Green Hub Model III (Modified To Get V4.3)99                      |

| 5.1.1 PV System100                                                    |

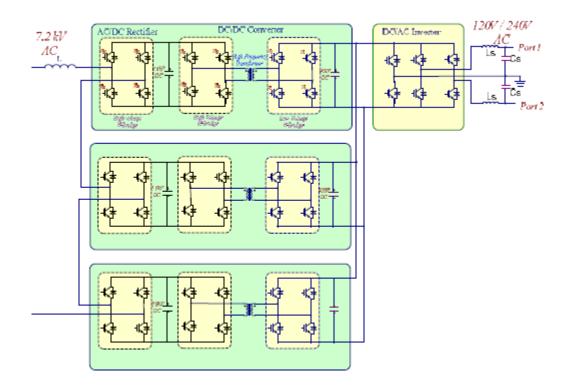

| 5.1.2 Solid State Transformers                                        |

| 5.1.3 Results                                                         |

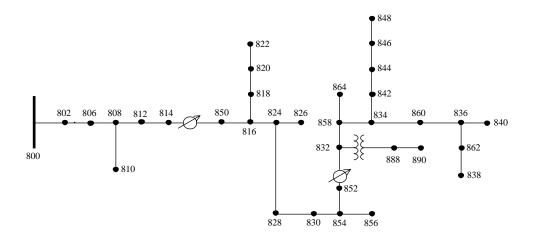

| 5.2 IEEE34 Test System                                                |

|                                                                       |

Page

CHAPTER

5.2.1 Background On IEEE34 Test System ......105

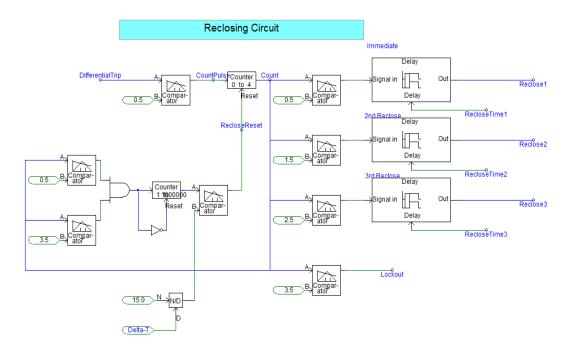

5.3 Reclosing Algorithm In PSCAD ......112

| CHAPTER | Page                                                                  |

|---------|-----------------------------------------------------------------------|

|         | 5.4 Implementation Of The Pilot Protection Scheme For The Large Scale |

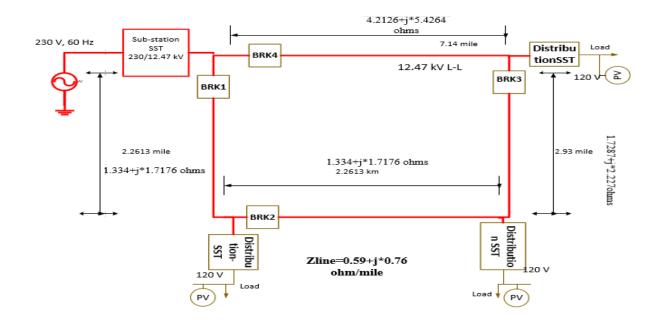

|      | System Simulation Loop Or Modified IEEE 34 System114                  |

|------|-----------------------------------------------------------------------|

|      | 5.4.1 Development Of The Modified IEEE 34 Loop (LSS Loop) From        |

|      | 24.9KU To 12.47KL Line To Line Voltage114                             |

|      | 5.4.2 Solid State Transformer Module Development116                   |

|      | 5.4.3 Implementation Of The Pilot Protection System For The LSS       |

|      | System Or The Modified IEEE 34 System122                              |

|      | 5.5 Implementation Of The Pilot Protection System For The Solid State |

|      | Transformer Model Developed At FSU At Both Substation Type And Load   |

|      | Type SST128                                                           |

|      | 5.6 Modified LSSS Model                                               |

|      | 5.6.1 Modified LSSS Model Design136                                   |

|      | 5.6.2 Results                                                         |

|      |                                                                       |

| 6    | CONCLUSIONS AND FUTURE WORK                                           |

|      | 6.1 Main Conclusions                                                  |

|      | 6.2 Future Work                                                       |

| REFE | RENCES                                                                |

| APPE | NDIX                                                                  |

| A    | pscad simulation files for chp 2,3,4                                  |

| В    | pscad simulation files for chp 5                                      |

# LIST OF TABLES

| Table                                                                  | Page                    |

|------------------------------------------------------------------------|-------------------------|

| Table 3.1: Pre Fault And Fault Condition Currents                      | 47                      |

| Table 3.2: CT Output Current                                           | 47                      |

| Table 3.3. Maximum Measurement Modules Supported At 1200H              | Iz And 600Hz Sampling   |

| Speed For Crio-9022                                                    | 57                      |

| Table 3.4. Maximum Measurement Modules Supported At 1200H              | Iz And 600Hz Sampling   |

| Speed For PXI-8106                                                     | 58                      |

| Table 3.5. Slave Cycle Limitations For NI 9144 Chassis With N          | I 9215 Modules59        |

| Table 3.6. System Reliability Test Results                             | 66                      |

| Table 3.7. Delay For Various Positions Of Fault [30]                   | 74                      |

| Table 3.8. Delay For Various Positions Of Fault [30]                   | 78                      |

| Table 3.9: Time Taken For Trip Signal Generation [30]                  | 81                      |

| Table 4.1. Statistical Summary Of The Dual Slope Method Base           | ed On 17 Runs91         |

| Table 4.2. Statistical Summary Of The Dual Slope Method Ba             | ased On 17 Runs. Tfault |

| Represents The Fault Timing, T_Trip Represents The Trip Signal Respons | se And The Delay Table  |

| Is The Timing Difference Between The Two.                              | 93                      |

| Table 4.3. The Trip Signal Delay Timings For The Pilot Protection      | System On The Tested    |

| Circuit For CT Ratio 20:2                                              | 103                     |

| Table 4.4. The Trip Signal Delay Timings For The Pilot Protection      | System On The Tested    |

| Circuit For CT Ratio 200: 20.                                          | 104                     |

| Table                                                                   | Page                 |

|-------------------------------------------------------------------------|----------------------|

| Table 5.1. Trip Signal Timing Results For Faults In Various Locations W | 7ith 8 Loads In Zono |

|                                                                         | 2113                 |

| Table 5.2. Trip Signal Delay Times For The IEEE34 Model For Zones 1     | , 5 And 6 [29] 119   |

| Table 5.3. Load Information For The 12.47 Kv System [38]                | 123                  |

| Table 5.4. Distribution SST Placement On Various Nodes Of The Mo        | odifies LSSS Systen  |

|                                                                         | [41]146              |

# LIST OF FIGURES

| Figure |                                                                                 | Page          |

|--------|---------------------------------------------------------------------------------|---------------|

|        | 1.1 Brief Introduction                                                          | 1             |

|        | 1.1. Energy Consumption from 1775-2011 (taken directly from [1])                | 2             |

|        | 1.2. FREEDM System (taken directly from [3])                                    | 4             |

|        | 1.3 Figure of the FREEDM system (taken directly from [4])                       | 5             |

|        | 2.1. SST topology [13]                                                          | 12            |

|        | 2.2. Equivalent average model [13]                                              | 14            |

|        | 2.3. Dq controller for rectifier [13]                                           | 16            |

|        | 2.4. Dual active bridge [13]                                                    | 16            |

|        | 2.5. DC/AC inverter topology [13]                                               | 18            |

|        | 2.6. Protection Zones in a power system [6]                                     | 20            |

|        | 2.7. is the graph for a general inverse-time—overcurrent relay characteristic   | es23          |

|        | 2.8. Currents in the differential system during normal operating condition      | when there is |

|        | no fault [17]                                                                   | 24            |

|        | 2.9. Currents in the differential system during in case of external fault [17]  | 24            |

|        | 2.10. Currents in the differential system during in case of internal fault [17] | 7]24          |

|        | 2.11. Percentage differential relay schematic (18)                              | 25            |

|        | 2.12. Common percentage differential protection characteristic [6]              | 26            |

|        | 2.13. Topology schematic of pilot protection [19]                               | 27            |

|        | 2.14. Directional relay operating characteristics [6]                           | 28            |

|        | 3.1. FREEDM model with multiple levels of control put reference [24]            | 34            |

| Figure                                                       | Page                      |

|--------------------------------------------------------------|---------------------------|

| 3.2. IFM zones of protection strategy [4]                    | 36                        |

| 3.3. Alternate concept of the IFM zones of protection in     | FREEDM [5]37              |

| 3.4. IFM system with the in cooperation of the AMUs          | 39                        |

| 3.5. Schematic of protection system explained above [12      | 2]40                      |

| 3.6. Differential current protection circuit diagram put re  | eference [6]41            |

| 3.7. Slope percentage characteristic [12]                    | 42                        |

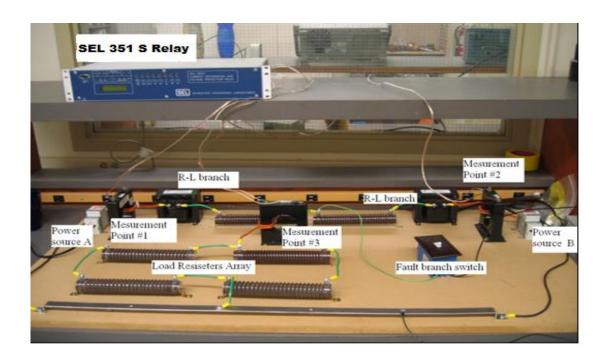

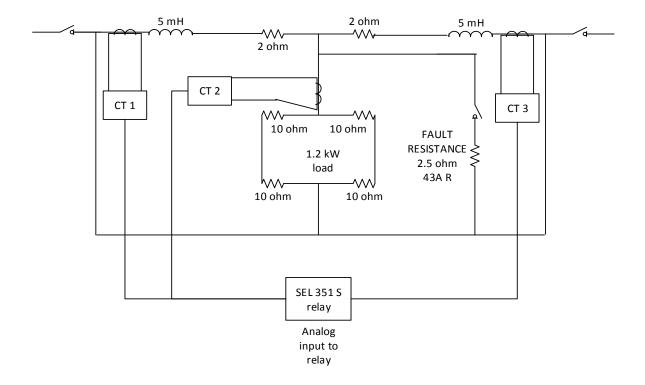

| 3.8. Single phase test setup for the SEL 351S relay          | 45                        |

| 3.9. Schematics of the test setup for the SEL 351 S relay    | 46                        |

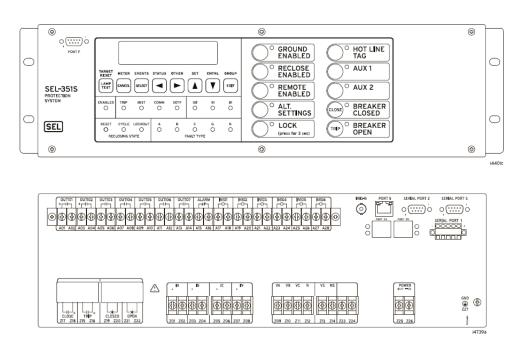

| 3.10. SEL 351 S schematic for front and back panel [25]      | 48                        |

| 3.11. Fault inception and detection timing as shown in the   | ne AcSELerator software49 |

| 3.12. Counter method algorithm                               | 51                        |

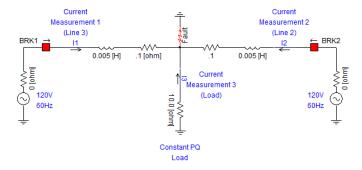

| 3.13. Test set up for simulation is PSCAD                    | 53                        |

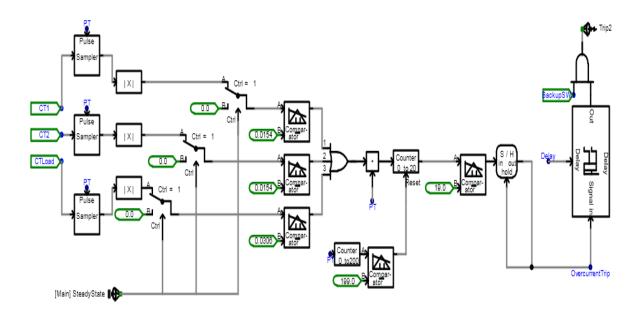

| 3.14. Pilot differential protection using the counter method | od54                      |

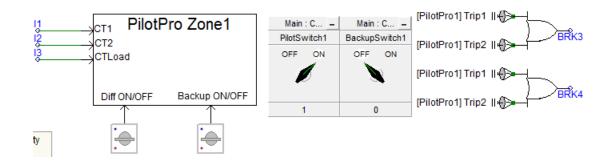

| 3.15. Backup Overcurrent Protection PSCAD Circuit            | 56                        |

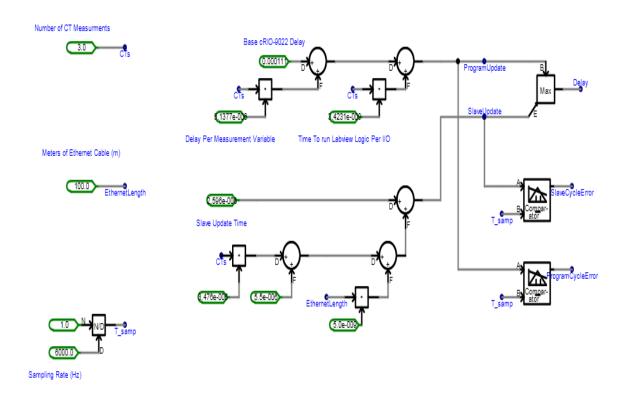

| 3.16. Hardware/Communication Delay Computation Cir           | cuit60                    |

| 3.17. 4 Load Communication/Processing Delay                  | 61                        |

| 3.18. 8 Load Communication/Processing Delay                  | 62                        |

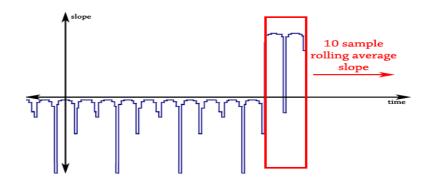

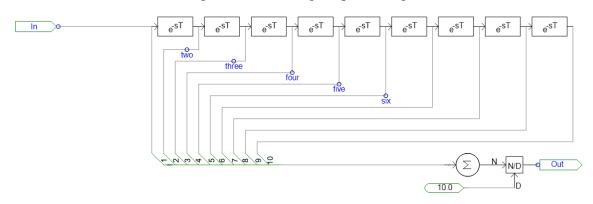

| 3.19. Rolling Slope Average                                  | 63                        |

| 3.20. 10 Sample Rolling Average Block [29]                   | 63                        |

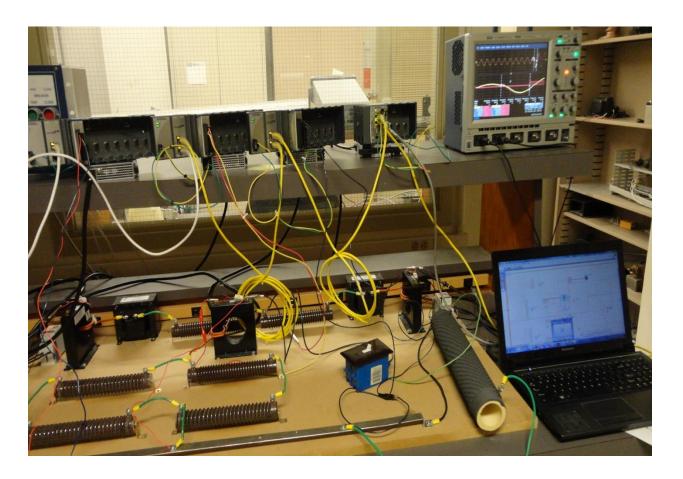

| 3.21: Picture of the NI hardware as connected on the test    | z-bed [30]69              |

| 3.22. Flow of data                                           | 70                        |

| Figure                                                                                                         |

|----------------------------------------------------------------------------------------------------------------|

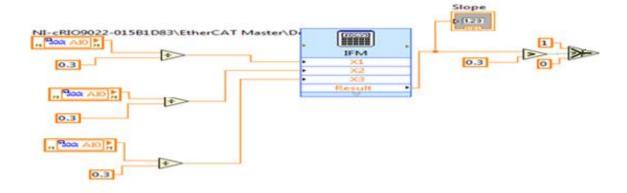

| 3.23. Example of the differential protection algorithm in Lab View software [30]71                             |

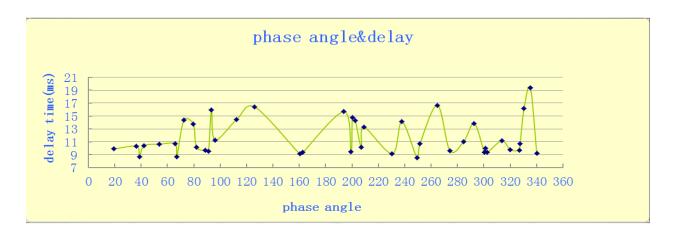

| 3.24. Delay vs phase angle graphical representation [30]                                                       |

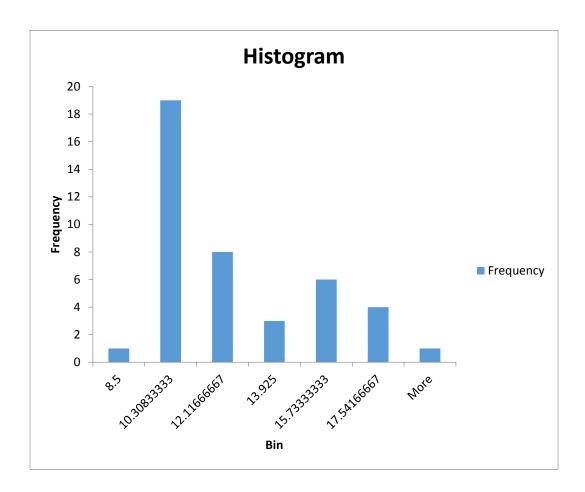

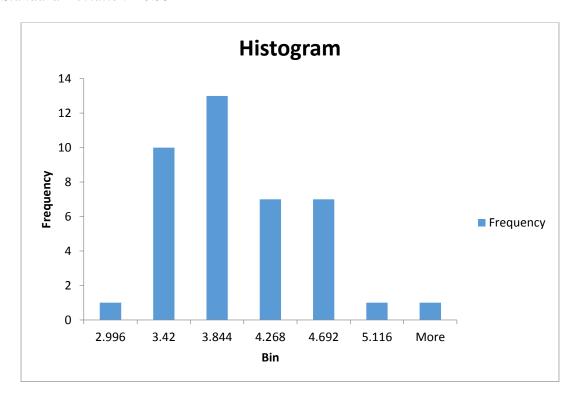

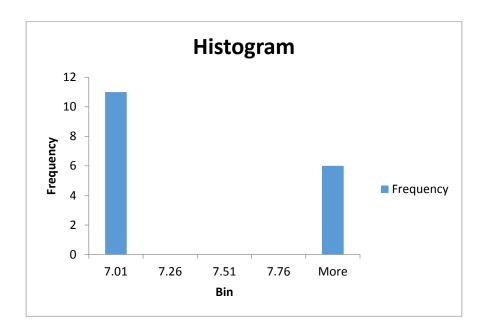

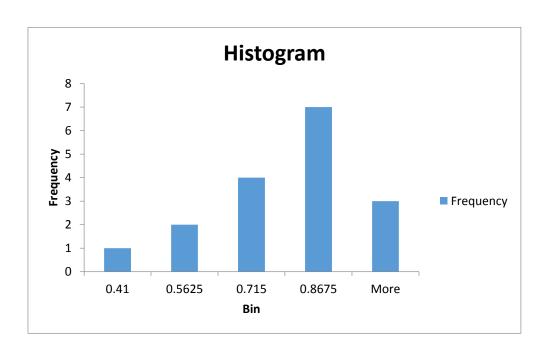

| 3.25 Histogram data for trip delay times for the timer and counter method77                                    |

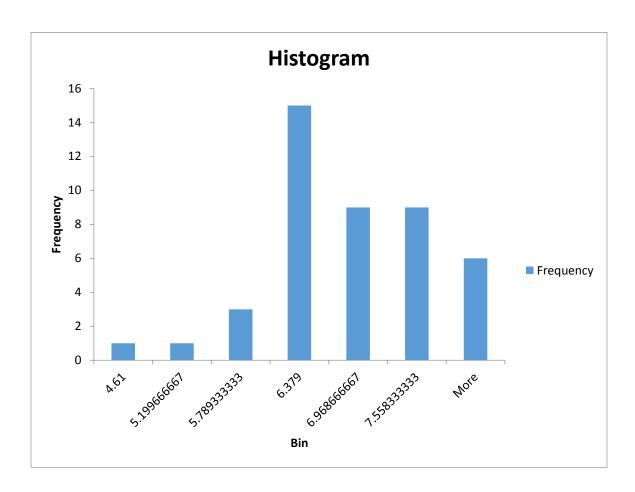

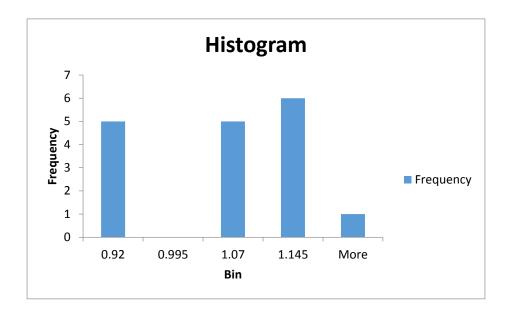

| 3.26 Histogram data for trip delay times for the 10 sample rolling window method80                             |

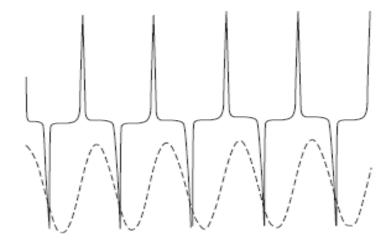

| 3.27 Histogram data for trip delay times for the 10 sample rolling window method is                            |

| shown for the FPGA method83                                                                                    |

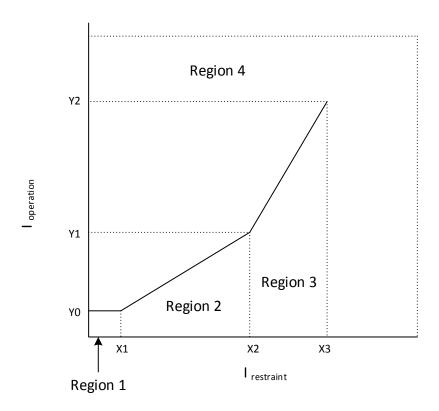

| 4.1. Multi slope differential protection characteristic curve85                                                |

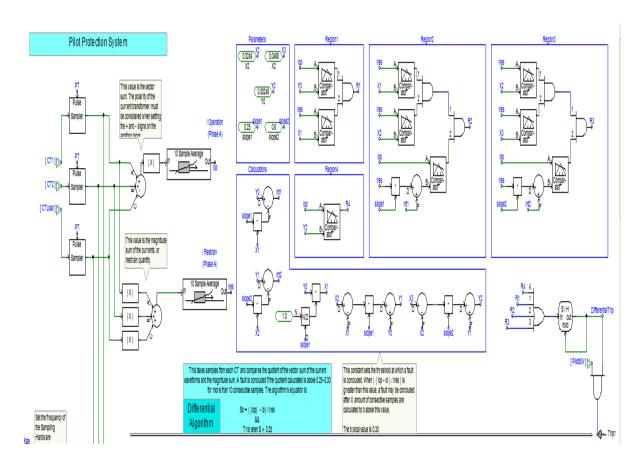

| 4.2. Algorithm for the multi slope differential characteristic in PSCAD89                                      |

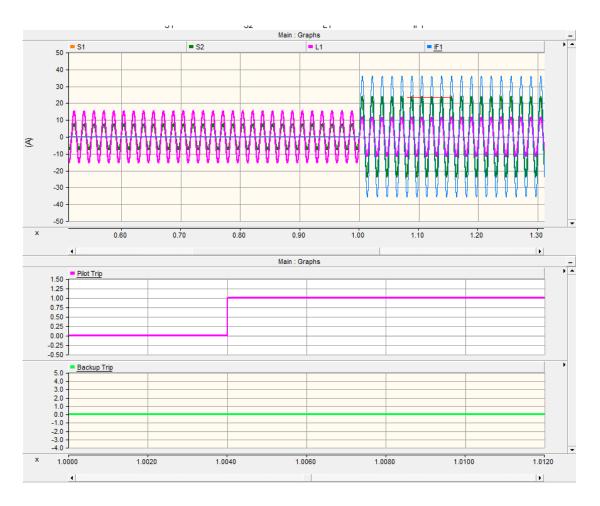

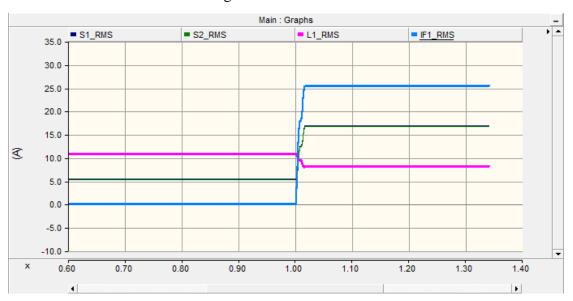

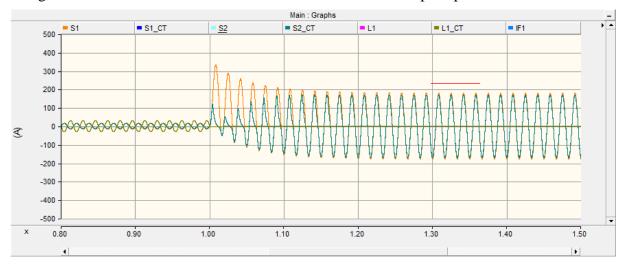

| 4.3. S1, S2 are the source currents while L1, IF1 are the source and fault current respectively.               |

| The trip timings for the dual slope pilot differential trip is shown in the figure for fault at t=1 sec.       |

| 90                                                                                                             |

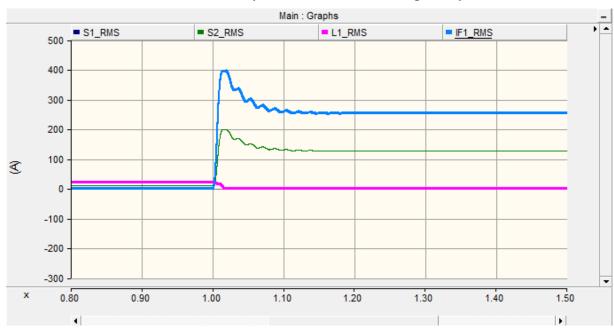

| 4.4. S1_RMS, S2_RMS are the source RMS currents while L1_RMS, IF1_RMS are the source                           |

| and fault RMS currents respectively90                                                                          |

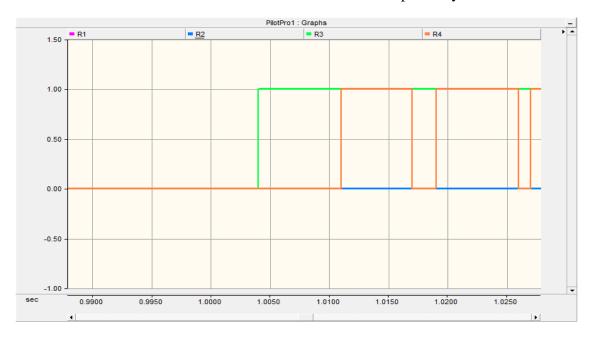

| 4.5. Digital bits R1, R2, R3 and R4 are shown going high after fault at t=1sec91                               |

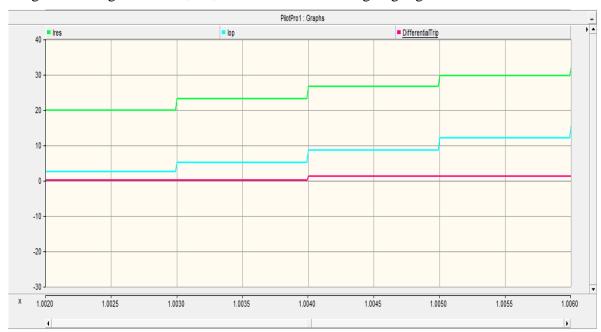

| 4.6. This shows the <i>Ioperation</i> , <i>Irestraint</i> calculation on graph and differential trip signal at |

| fault at t=1 sec91                                                                                             |

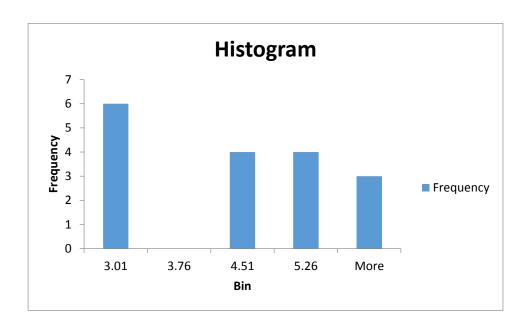

| 4.7 Histogram for trip timing delay for the dual slope method                                                  |

| 4.8 Histogram for trip timing delay for previous 10 sample rolling window method95                             |

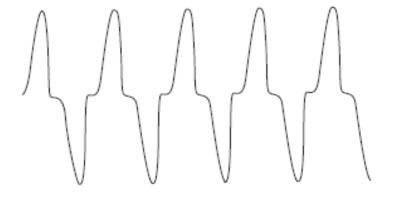

| 4.9. CT output with no saturation [6]97                                                                        |

| Figure                                                                                              |

|-----------------------------------------------------------------------------------------------------|

| 4.10. CT output with part saturation [6]97                                                          |

| 4.11. CT output with severe saturation [6]                                                          |

| 4.12. CT primary and secondary winding [32]98                                                       |

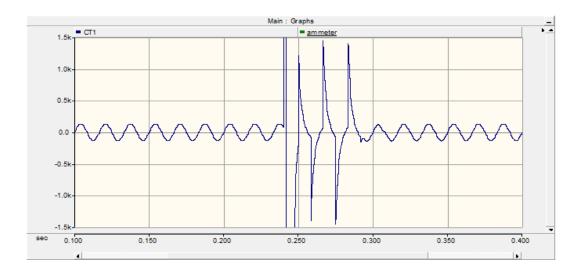

| 4.13. CT secondary current for ratio 2:20 for the CT, fault current for a 100kV, 1000 ohm load 1    |

| phase system actual and saturated current reading                                                   |

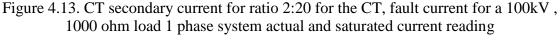

| 4.14. Actual circuit current for ratio 2:20 for the CT, fault current for a 100kV , 1000 ohm load 1 |

| phase system actual and saturated current reading                                                   |

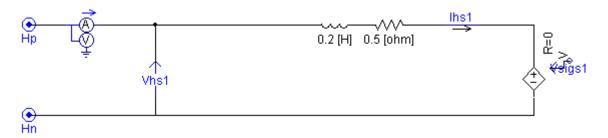

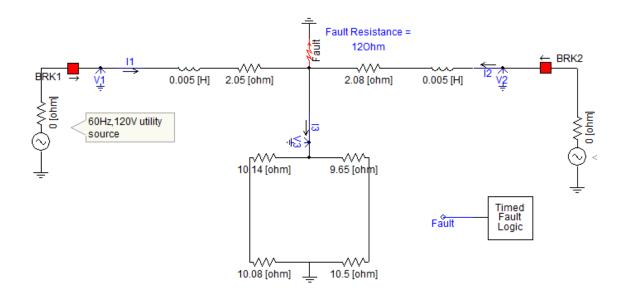

| 4.15. Test bed circuit for the CT saturation test for the pilot protection module101                |

| 4.16. S1, S2 and L1 are actual currents on the primary while S1_CT,S2_CT and L1_CT are              |

| secondary CT currents referred to primary                                                           |

| 4.17. Rms currents through the system before and after fault                                        |

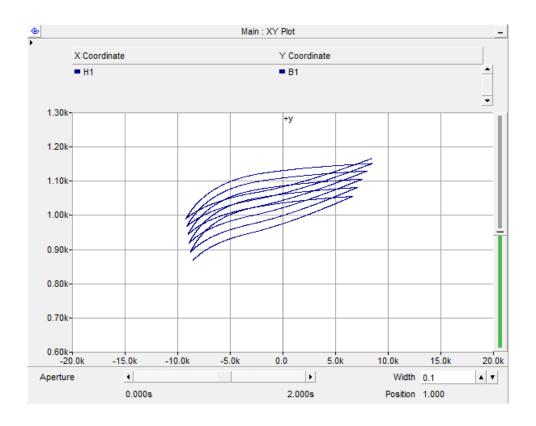

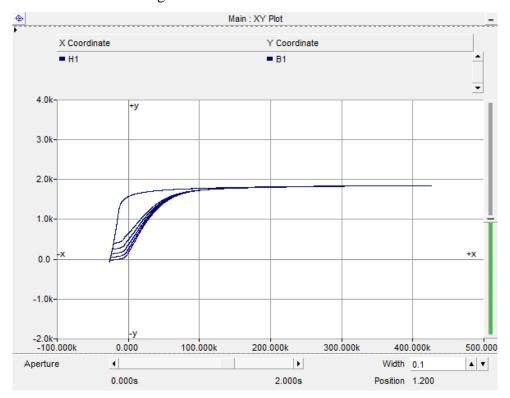

| 4.18. BH curve before fault                                                                         |

| 4.19. BH curve after fault                                                                          |

| 4.20 Histogram for trip timings for the pilot protection system on the tested circuit for CT ratio  |

| 20:2104                                                                                             |

| 4.21 Histogram for trip timings for the pilot protection system on the tested circuit for CT ratio  |

| 200:20 105                                                                                          |

| 5.1. Green Hub 3 system diagram [35]                                                                |

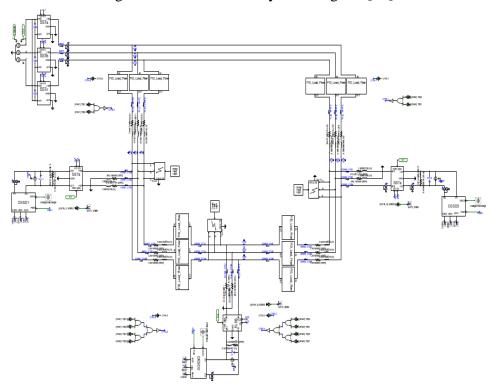

| 5.2. Green hub model v4.3 in PSCAD [36]                                                             |

| Figure                                                                                           | e   |  |

|--------------------------------------------------------------------------------------------------|-----|--|

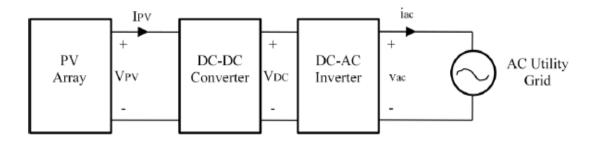

| 5.3. Topology of the PV system [35]                                                              | .08 |  |

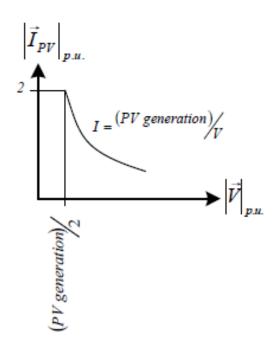

| 5.4. VI characteristic curve of the PV [35]                                                      | .08 |  |

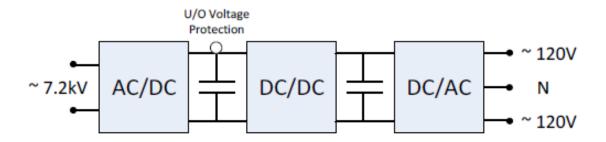

| 5.5. Topology of the SST [35]1                                                                   | .09 |  |

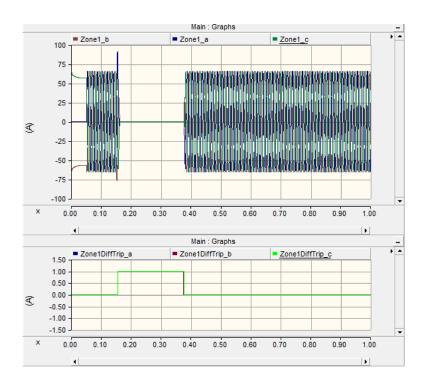

| 5.7. Pilot protection module in PSCAD                                                            | .11 |  |

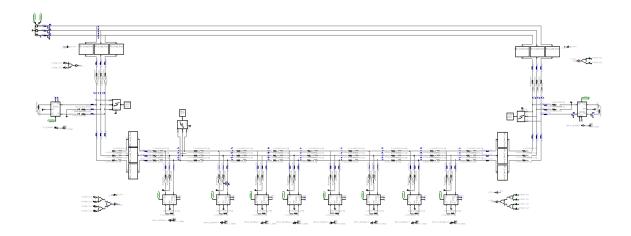

| 5.8. Modified Green Hub v4.3 with 8 SSTs in Zone 21                                              | .12 |  |

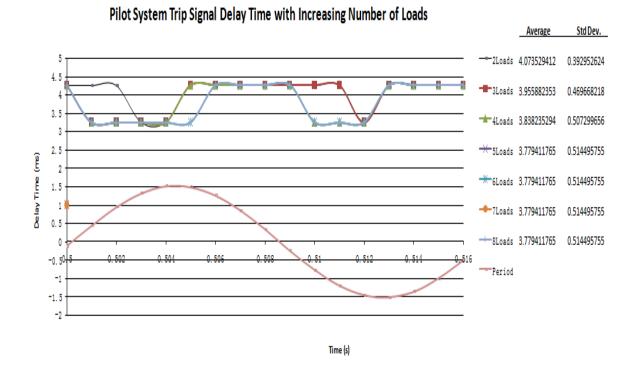

| 5.9. 1000Hz Differential Trip Signal Timing Results With Increasing Number of SST/Loads          | in  |  |

| Zone 21                                                                                          | .13 |  |

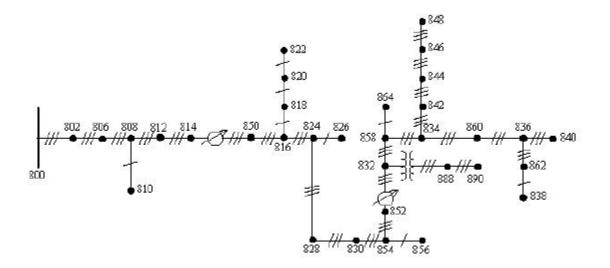

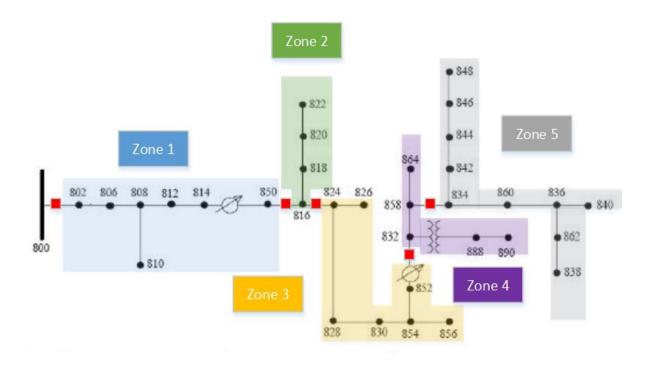

| 5.10. IEEE34 node test feeder schematic [37]                                                     | 15  |  |

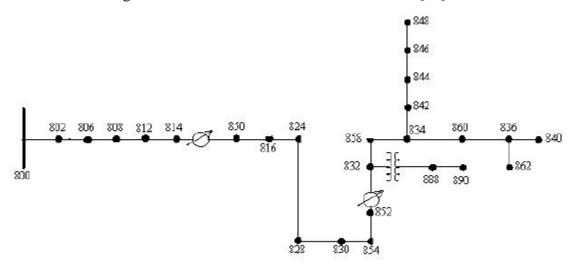

| 5.11. Three phase main feeder for the IEEE34 test system after simplification [37]1              | .15 |  |

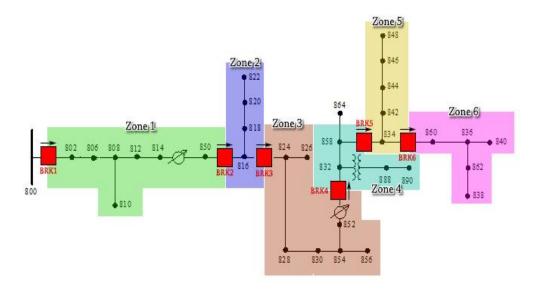

| 5.12. Zones of protection for the pilot protection system for the IEEE34 model [29].1            | .16 |  |

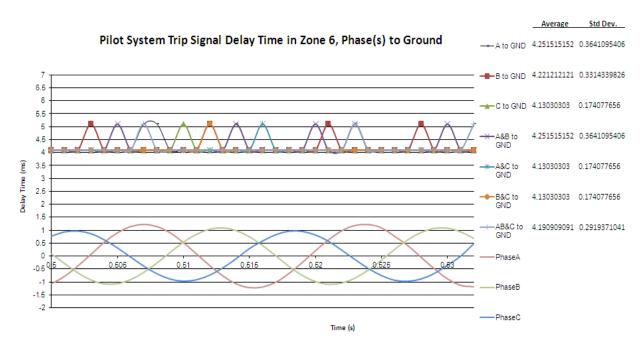

| 5.13. Zone 6 Trip delay times for single line to ground, double line to ground and 3 phase fault |     |  |

| 1                                                                                                | .17 |  |

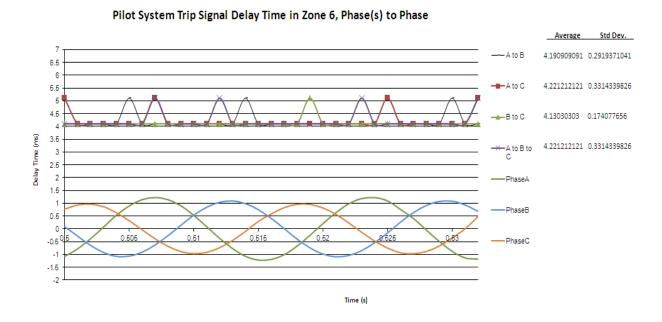

| 5.14. Zone 6 Trip delay times for line to line faults                                            | 18  |  |

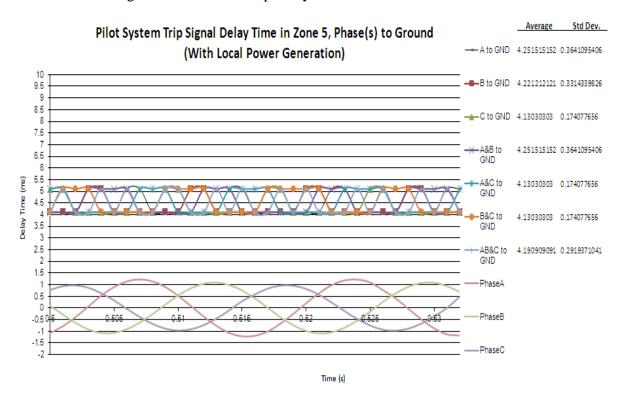

| 5.15. Zone 5 Trip delay times for single line to ground, double line to ground and 3 phase fa    | ult |  |

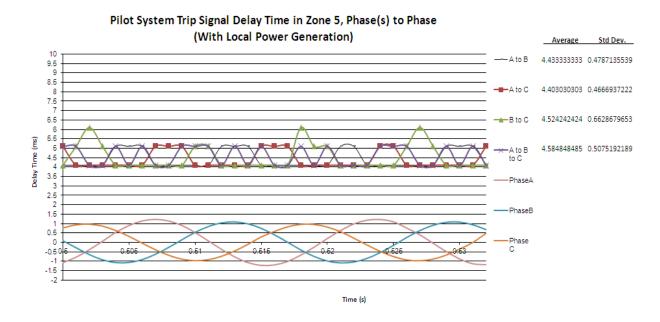

| 1                                                                                                | .18 |  |

| 5.16. Zone 6 Trip delay times for line to line faults                                            | 19  |  |

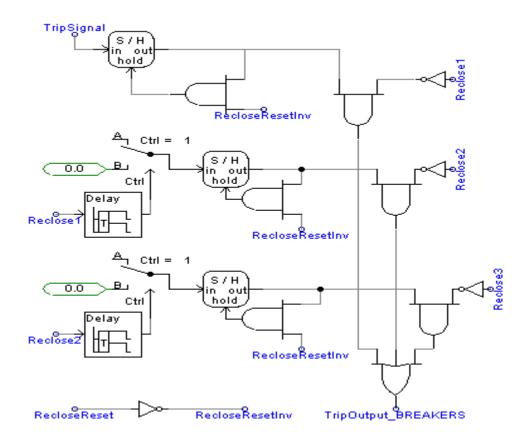

| 5.17. Reclosing logic included with the trip logic [29]                                          | .21 |  |

| 5.18. Logic to determine reclosing timings 1, 2 and 31                                           | .22 |  |

| 5.19. IEEE 34 (original model) schematics [37]                                                   | 23  |  |

| Figure                                                                                            |

|---------------------------------------------------------------------------------------------------|

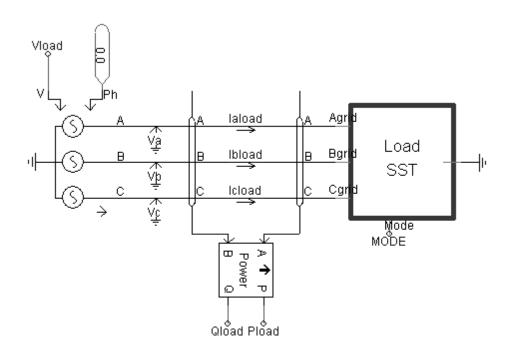

| 20. The figure above represents active rectification i.e. nonlinear rectified with power electron |

| switches [38]                                                                                     |

| 5.21. SST topology used for the average model simulation [13]                                     |

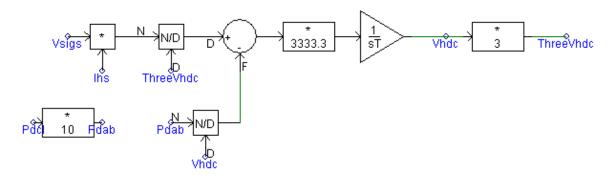

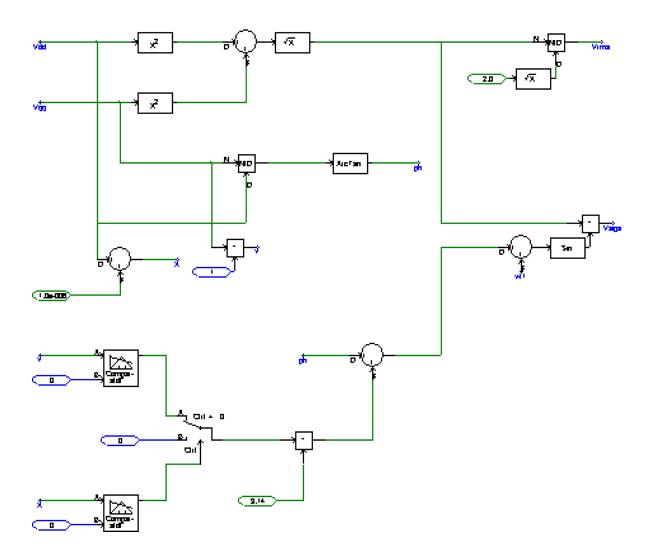

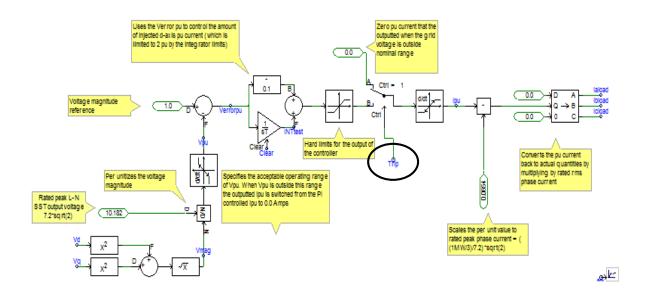

| 5.22. Power balance equation block for the rectifier [38]                                         |

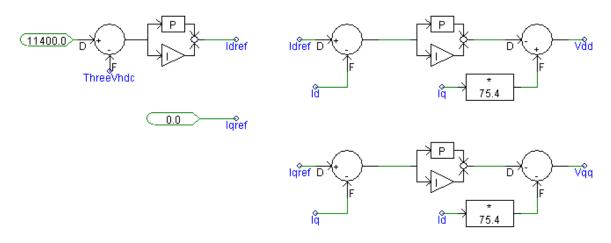

| 5.23. Control Stage in rectifier [38]                                                             |

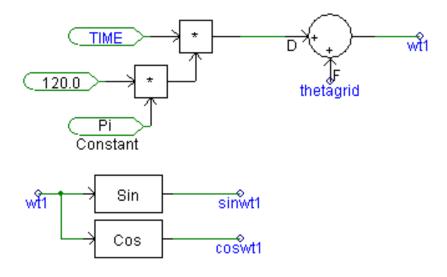

| 5.24. Calculating $\omega t$ angle using grid voltage angle [38]                                  |

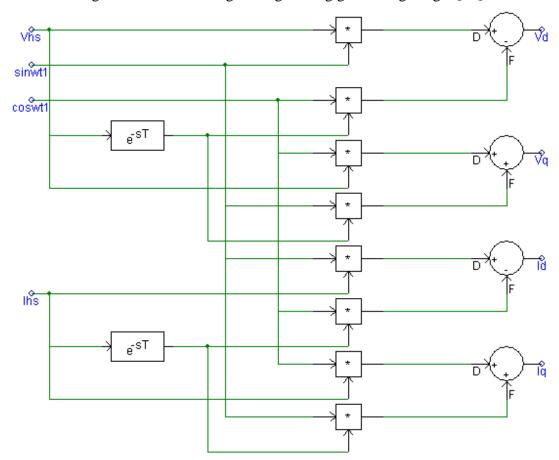

| 5.25. <i>Id</i> , <i>Iq</i> Calculations [38]                                                     |

| 5.26. Vdd and Vqq Calculation [38]13                                                              |

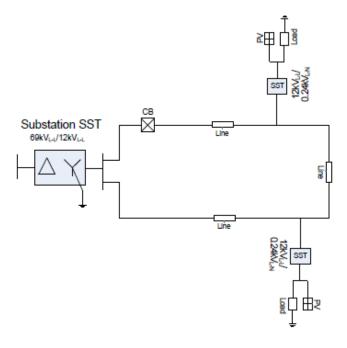

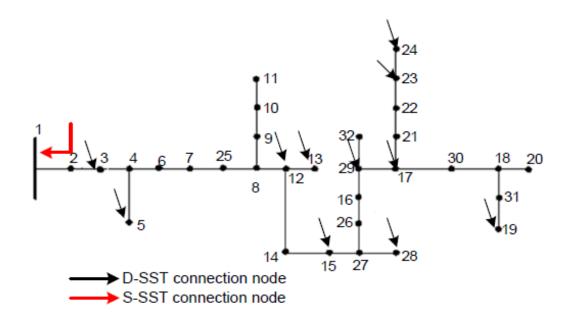

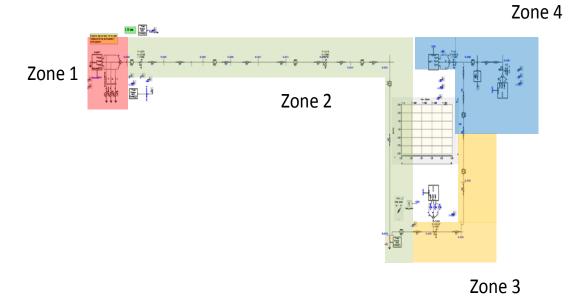

| .27. Zones of protection for implementing the pilot protection system for the LSSS system [39     |

| 13                                                                                                |

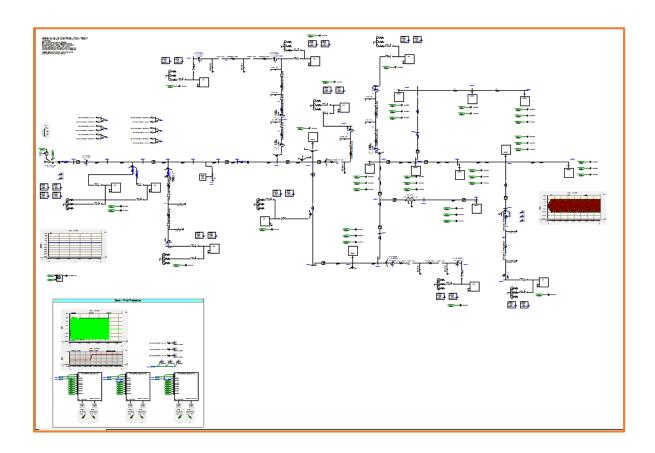

| 5.28. Schematic of LSSS loop on PSCAD                                                             |

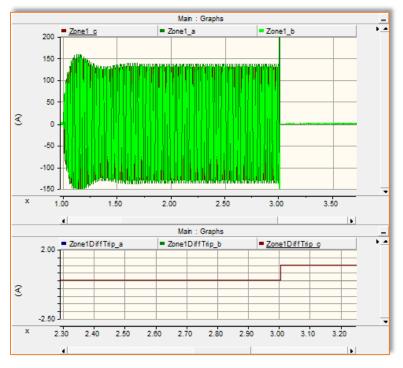

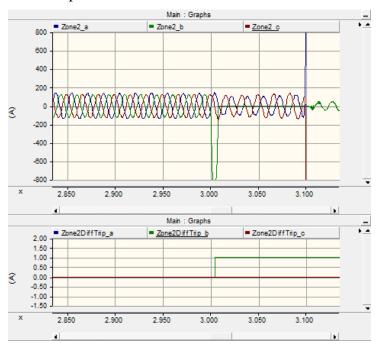

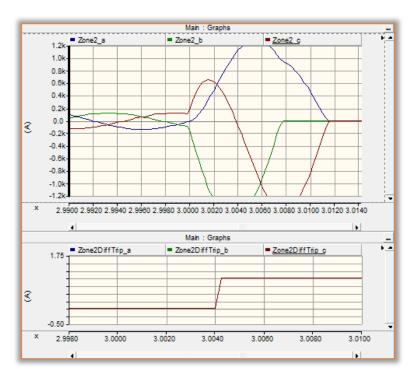

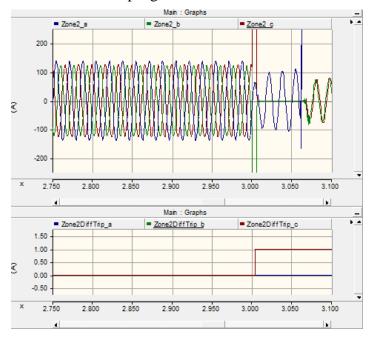

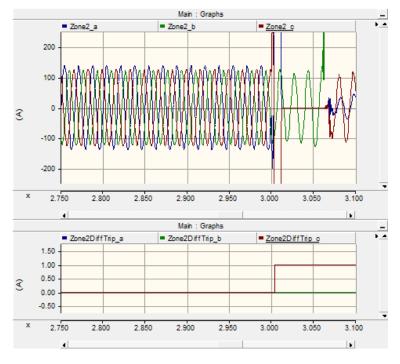

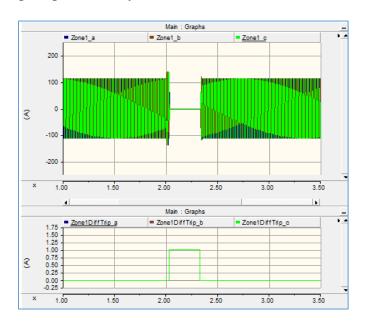

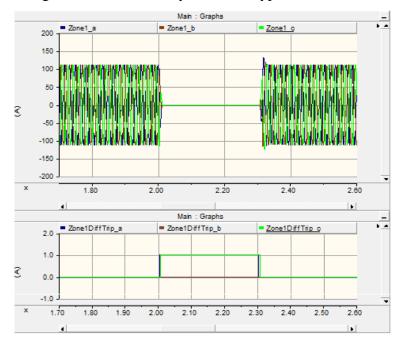

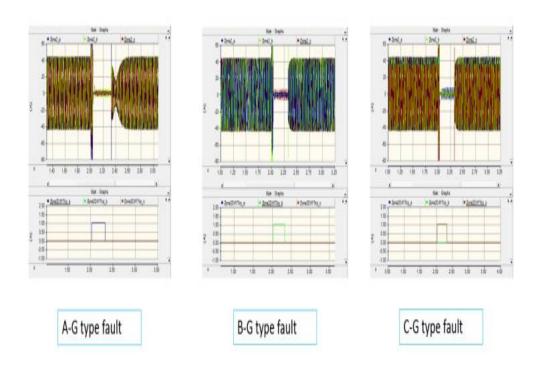

| 5.29. Three phase fault in Zone 1 for IEEE 34 with SST at time 3 sec                              |

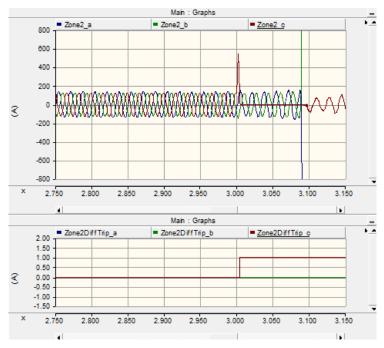

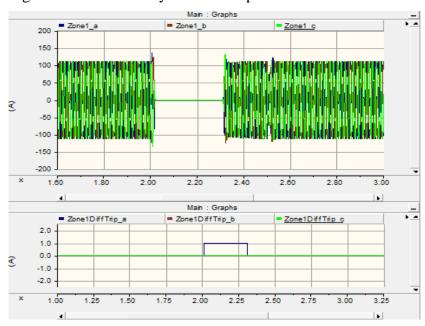

| 5.30. Phase B to ground fault in Zone 2 for IEEE 34 with SST at time 3 sec                        |

| 5.31. Phase C to ground fault in Zone 2 for IEEE 34 with SST at time 3 sec                        |

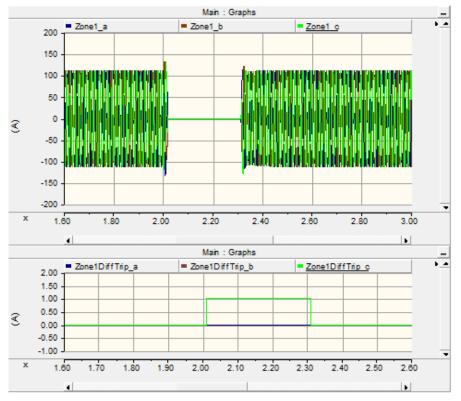

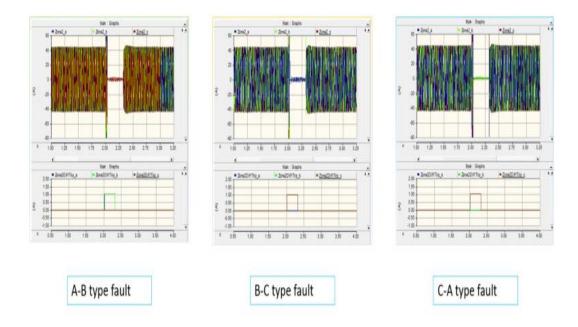

| 5.32. Phase A to B fault in Zone 2 for IEEE 34 with SST at time 3 sec                             |

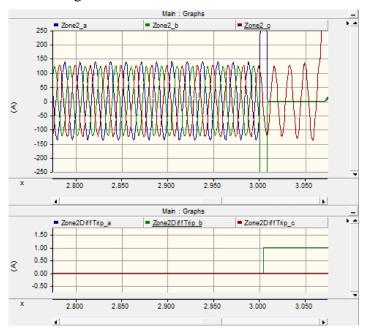

| 5.33. Zoom in on the trip signal activation for a fault at t=3 sec in zone 2                      |

| 5.34. Phase B to C fault in Zone 2 for IEEE 34 with SST for fault at time 3 sec13                 |

| 5.35. Phase C to A fault in Zone 2 for IEEE 34 with SST for fault at time 3 sec13                 |

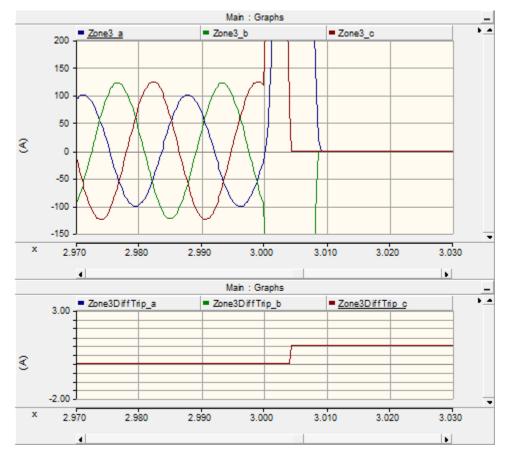

| 5.36. 3 phase fault in Zone 3 for IEEE 34 with SST for fault at time 3 sec                        |

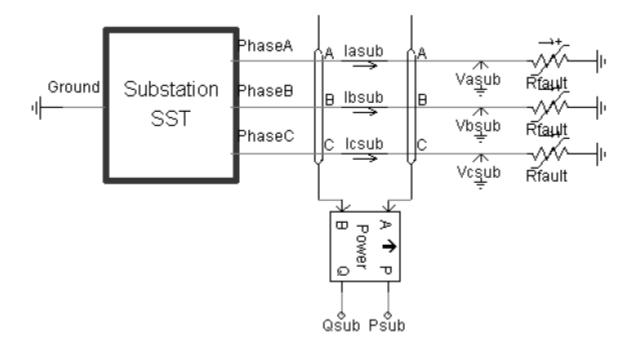

| 5.37. Test circuit for the SST model [40]                                                         |

| Figure                                                                                               |

|------------------------------------------------------------------------------------------------------|

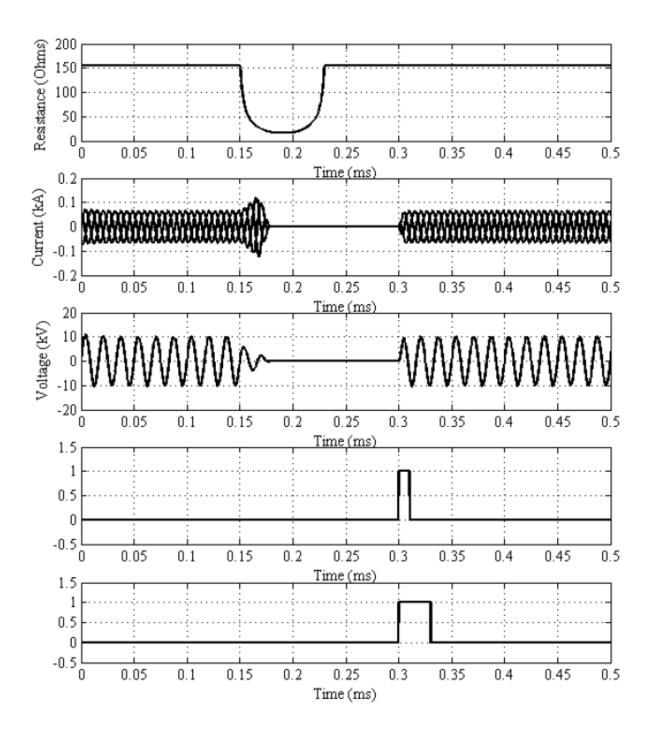

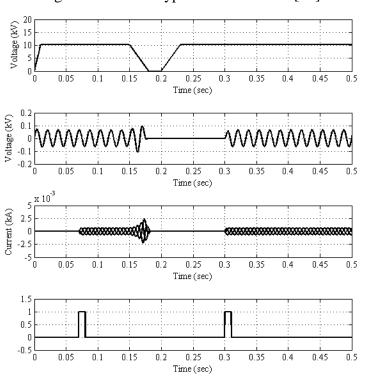

| 5.38. Substation SST behavior for faulted condition to check upon injected current I, grid voltage   |

| V, PI clear (clearsubtime) and substation SST reset signal (resetsubtime) [40]140                    |

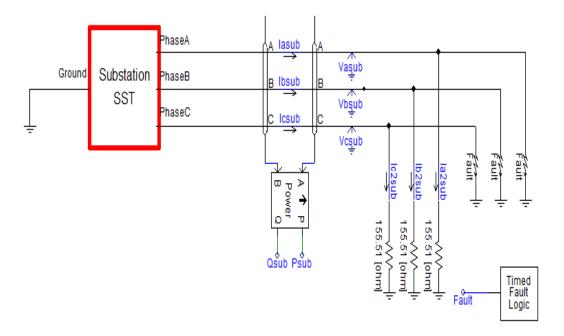

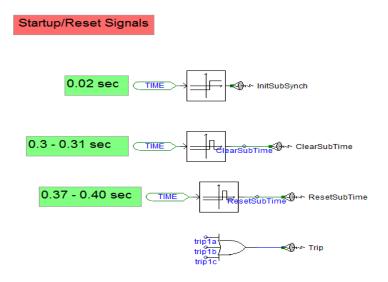

| 5.39. Circuit diagram for applying pilot protection to the substation SST141                         |

| 5.40. Signals required by the substation SST for fault clearing and reclosing141                     |

| The substation SST has three major signal                                                            |

| 5.41. Trip signal from pilot protection being utilized for clearing the fault for the substation SST |

| 142                                                                                                  |

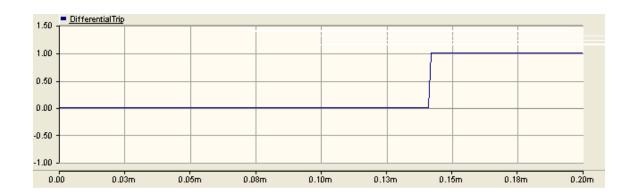

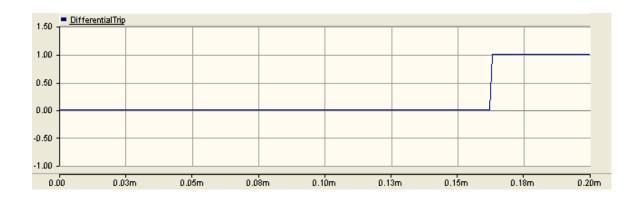

| 5.42. The fault is successfully detected at 0.18 second and cleared 0.37 second (successfully) for   |

| substation type SST                                                                                  |

| 5.43. Load type SST test circuit [40]144                                                             |

| 5.44. Characteristic of the load type SST during faulted condition. User defined grid voltage        |

| profile, grid voltage, injected current and the reset signals are shown here [40]145                 |

| 5.45. Schematic of the modification made to the original IEEE 34 and the placement of D-SSTs is      |

| also shown here [41]146                                                                              |

| 5.46. Zones of protection for the implementation of the pilot protection system for the modified     |

| LSSS loop system [41]                                                                                |

| 5.47. Fault Analysis for three phase bolted fault in zone 1                                          |

| 5.48. Fault Analysis for AB type fault in zone 1                                                     |

| 5.49 Fault Δnalysis for RC type fault in zone 1                                                      |

| Figure                                           | Page |

|--------------------------------------------------|------|

| 5.50. Fault Analysis for CA type fault in zone 1 | 150  |

| 5.51. Zone 2 faults for A-B, B-C, and C-A Faults | 150  |

| 5.52. Zone 2 faults for A-G, B-G, and C-G Faults | 151  |

#### LIST OF SYMBOLS

Α Ampere A/D Analog to Digital Converter AC **Alternating Current** Address Resolution Protocol **ARP** CT**Current Transformer** Voltage gradient with respect to time dvdt D/A Digital to Analog Converter DAQ **Data Acquisition System** DC Direct Current **DESD** Distributed Energy Storage Device DGI Distributed Grid Intelligence **DHCP** Dynamic Host Control Protocol **ESD Energy Storage Device FCL Fault Current Limiter** FID Fault Isolation Device FREEDM Future Renewable Electric Energy Delivery and Management **GPS Global Positioning Satellite IEEE** Institute of Electrical and Electronics Engineers **IEM Intelligent Energy Management IFM** Intelligent Fault Management **IGBT** Insulated-gate Bipolar Transistor ΙP Internet Protocol IRIG Inter-range Instrumentation Group  $J_{c}$ Critical Current density of Superconductor k Kilo  $(1x10^3)$ kA Kilo Ampere kbyte Kilo Byte

kOhm Kilo Ohm

kV Kilo Volt

kVA Kilo Volt Ampere

K Kelvin

m Milli (1x10-3)

mH Milli Henry

ms Milli Second

mV Milli Volt

M Mega (1x106)

Mbps Mega bits per second

MHz Mega Hertz

MS Microsoft

MVA Mega Volt Ampere

MW Mega Watt

n Nano (1x10-9)

ns Nano Second

NSF National Science Foundation

OP AMP Operational Amplifier

p.u. Per unit

rms Root mean square

RC Resistor-Capacitor

RSC Reliable and Secured Communication

SNTP Simple Network Time Protocol

s Seconds

SEL Schweitzer Engineering Laboratories Company

SST Solid State Transformer

TCP Transmission Control Protocol

u Micro (1x10-6)

uF Micro Farad

uH Micro Henry

US United States of America

V Volt

W Watt

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Brief Introduction

• In the future, the need for power will increase so will the need to increase power generation.

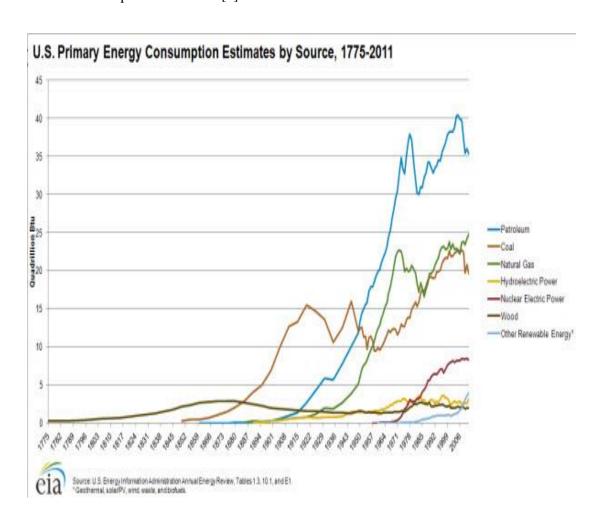

Renewable energy is a very interesting and upcoming field. There is a growing interest to develop distributed renewable electric generation, distributed control of energy management and also energy storage. The graph below shows the US primary energy consumption since 1775 [1].

- Figure 1.1. Energy Consumption from 1775-2011 (taken directly from [1])

- Thus the in the future we will have lot of renewable resources contributing to the grid. But creating all renewable grids can not only be expensive, but would require new expertise and resources for integrating these sources into the grid. It would rather be more efficient to connect renewable energy sources to existing distribution grids.

- But these renewable energy sources have a lot of power electronic devices used in them

like inverters, rectifiers, dc-dc converters; also these power electronic devices change the

voltage as well as current profile due to which these devices bring new issues and

challenges to the protection system.

- The Fault characteristics of power electronic devices is very different from traditional distribution systems like the fault level in a solar PV panel inverter is so less that sometimes it cannot be even detected as a fault [2].

- Also the fault current level will also be limited due to these devices as well, and also other issues like power harmonics can come into play [2].

- So in the future we are looking at a grid which will be a modernized electrical grid that uses information and communications technology to gather and act on information, so as to balance the generation of both renewable as well as non-renewable sources of energy.

There by providing protection concepts for such smart grids will be the next step.

The FREEDM loop, a National Science Foundation (NSF) enterprise, is an experimental power grid which aims to provide a few answers and solution to these question asked. It claims to remove the requirement for enhancing the existing power system equipment at the distribution level and also talks about the renewable energy generation and distribution concerns. The inclusion of many new loads with renewable energy will place an added pressure on the electrical infrastructure. The FREEDM system's plan is to operate

distributed generation and energy management through advanced power electronics and communications is demonstrated in this research topic [3].

#### 1.2 The FREEDM system

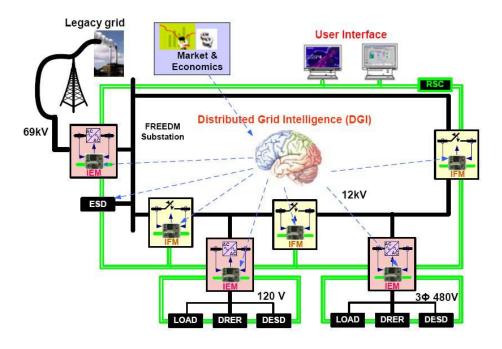

The FREEDM system was formulated as a grid infrastructure with not only renewable resources integrated in to the grid, but with capabilities to operate in faulted conditions (islanding), and capabilities to react to system depending upon the change in load, demand automatically based on the data received through digital communications. This system will help assimilation of renewable energy generation into the power system grid. The system helps us develop break-through technologies in energy storage, distributed grid intelligence and power semiconductor devices. To show the various research developments, a 1 MW green energy hub loop supplied by renewable energy resources is under development. The FREEDM system is designed at allowing the customers to plug in renewable resources that generate power but also use devices that have storage capabilities, such devices are placed at residences and commercial / industrial factories, and also has the ability to manage their energy consumption through the load management system [3]. A single line diagram of the proposed FREEDM system is shown in Figure 1.2.

Figure 1.2. FREEDM System (taken directly from [3])

The FREEDM system includes advanced power electronic features combined with information relaying technology to develop a futuristic distribution grid which will include many features. One of the features will be plug and play of DRER (Distributed Renewable Energy Resource) and DESD (Distributed Energy Storage Device). While managing such DRER's, DESD's and loads using DGI (Distributed Grid Intelligence). This system also include revolutionary solid devices like FID (Fault Isolation Devices) able to clear faults extremely fast. The distribution system has the capability of being totally isolated from the main grid and still run perfectly in the islanded mode of operation. [3].

Figure 1.3 Figure of the FREEDM system (taken directly from [4])

A figure of the FREEDM system is shown above. In this the loads are connected to 120 V AC regulated supply feeder. The DRER, DESD can be directly connected to the DC link of the SST. The SST is a 3 level/layer device which has AC-DC-AC link. So the SST is allowed bidirectional power flow control and controls other cases of power administration authority, fault current limitation and voltage ride through needed for dynamic plug and play system. An ultra-fast FID is used to isolate faults throughout the 12 kV system so as to supply uninterrupted good quality power to the consumer. All the FID's and the SST's coordination is done with the help of DGI or IEM (Intelligent Energy Management) software coded in each SST and FID. The DGI/IEM communicate with the SST's and FID's through the RSC (Reliable and Secured Communication network) [3]

• As shown in the figure 4, the system has FCL (Fault Current Limiters) places at various points in the loop system. The loads, DRERs and DESDs are joined to the loop through the SST's. The loop is then segregated in to different sections/zones. Each zone will contain a fixed number of SST's. And every zone is protected by FID which are the electronics CBs of the system.

The IFM (Intelligent Fault Management system) is used to help protect the FREEDM loop system by isolating faults in the 12 KV distribution system. The renewable sources and the storage devices are connected through the IEMs to the loop. Both the IEM and the IFM are connected through the RSC .In the event of a fault the FREEDM system can operate independently in the islanded mode of operation [5].

## 1.3 Motivation and Objective

The standard distribution system is framed in a branched layout and is protected by the traditional 3 division overcurrent protection: The primary grid feeder is protected by a circuit breaker at the substation terminal. In the middle section of a feeder a recloser is placed. Fuses are used to protect the smaller branch feeders in a normal distribution system. Using proper settings for coordination timings, each section contributes to the backup protection for the lower section. On occurrence of a fault on the main feeder, the entire feeder will have to shut down, and this is one of the biggest disadvantages of these types of protection schemes [6] On account of outage of fuses, momentary outages are caused which damage sensitive electronic component devices [6]. Most distribution systems are

radial systems. But because of DG, as fault current will be supplied by both the DG and the grid, in that case such systems are considered as loop systems. The FREEDM system is also such a loop system. Thus traditional over current protection systems cannot work and so the un-faulted DG feeder might trip.

For higher quality power closed loop distribution system are now being used. As a result fault in one section cannot cause outage down the line as in case of radial/open loop system. Moreover closed loop systems provide more rigid voltage support and has better capacity of load rising. Hence loop systems are an ideal choice for future distribution system [7] [8]. Conventional over current relays cannot be used because of bidirectional power flow in the network because of the presence of DG in the system. Also fault clear time will ensure whether DG's will lose stability or not. Moreover closed loop systems have higher short circuit currents and also increase the dips in voltage as well as frequency. Thus making these systems more sensitive to power system oscillations and fault expansion [7] [8].

The FREEDM grid being a smart grid, it will be able to operate for both grid connected condition as well as islanded condition. Such modes of operation question standard over current protection schemes for distribution systems. Hence it is extremely important to develop protection schemes that involve communications [9]. The challenges posed by protection systems in micro grids like the FREEDM system are the problems that are linked with bidirectional power flow, meshed structure and continuously changing level of fault current levels because of discontinuous attributes of the DGs and also reduced levels of fault current during islanded mode of operation [10] [11].

The other issue with the protection system is the operation time. The current distribution protection system can identification and interruption time is around more than a second. One of reasons for this could be that classical mechanical circuit breaker, are capable to turn off the fault current only at zero crossing current point, and hence the require at least a cycle to interrupt/cut off the circuit. The advancements of Solid State technology gives a rather unique explanation of interrupting a fault, i.e. the solid state circuit breaker (SSCB/FID) Fault isolation devices depend on swift switching solid state switches. SSCB/FID is able to interrupt fault current inside a millisecond because of its capability to switch thousands of times per second [12]. Based on this approach the differential pilot protection system was developed previously at ASU. The concept, theory, practical implementation of the pilot differential protection is shown in [12.].

The objective of this thesis is to implement the pilot differential protection system which complies with the brisk operation and precise fault isolation requirements of the multi-source FREEDM loop system, into larger distribution system so as to verify the results based on the hardware and the software simulations. Also the algorithms performance was evaluated based on a few changes made to the algorithm and test conducted on the test bed were compared to the simulated results.

#### **1.4 Thesis Outline**

The key content of this thesis has been divided into 6 Chapters. Chapter 1 provides an introduction of the key issues faced today and presents the answer in form of the pilot differential protection system. The background of the thesis on the FREEDM system is also explained in this chapter.

In Chapter 2, a complete literary analysis which includes stating problems and its mitigation strategies in the form of the pilot differential protection are presented. For a comparison of traditional protection scheme, common protection schemes are described. A contrast of the advantages and drawbacks of the proposed scheme are made.

Chapter 3 determines zonal protection, IFM (intelligent fault management) concepts as well as differential protection concept developed earlier. After that in Chapter 3, the existing over current protection standards used in distribution systems is tested on an existing industrial relay by setting up a scaled model of a protective zone and applying one of fastest commercial relay that has been used widely in the industry for over current protections i.e. the SEL351 S over current relay on it. The new pilot differential protection system (which includes both the counter method and the 10 sample average window concept) is shown by altering the original pilot protection algorithm later in the same chapter. The simulation results of the new algorithm on the same test bed on PSCAD are shown in this section of the chapter. Chapter 3 studies the implementation of the new algorithm on hardware system and the results of the hardware and the software simulations are then compared with the hardware results.

In Chapter 4 the new multi slope differential protection scheme formulation, testing, simulation and results are explained. Lastly in chapter 4 the effect of current saturation is explained and the results of the pilot protection system affected by current saturation are shown.

In Chapter 5, the implementation of the pilot protection system in the GreenHub model is explained and the results are discussed. Next the implementation of the pilot

protection system in the IEEE34 node system with PQ loads is discussed and the results shown. Later implementation of the pilot protection system in the modified IEEE34 node system or LSSS system with SST loads is discussed and the results tabulated. And lastly the working of the substation and load type SST developed at FSU and the role of the pilot protection system in its protection are explained. The results of the pilot protection system for the protection of the modified LSSS system utilizing the above mentioned SST models are also tabulated. In the end, the conclusions and possible extensions as future work are shown in Chapter 6.

Appendices A-C provides basic information on the studies carried out in this thesis. Appendix A is the PSCAD simulation files that are used for chapter 2 and 3 experiments for the test bed, dual slope/ point method, and the current saturation experiment. Appendix B presents the PSCAD simulation files for the GreenHub, IEEE 34, LSSS system and the modified LSSS system experiment.

#### **CHAPTER 2**

#### LITERATURE REVIEW

#### 2.1 Solid State Transformer [13]

The SST is used for active control and management of connected renewable resources and loads to its secondary. The primary side is connected to the FREEDM Loop. It is speculated that the SST will allow the increment in power delivery and power quality. The SST allows the plug in and generation of various DGs and also allows the increment/decrement of loads into the grids without having any detrimental effects.

## 2.1.1 SST Design [13]

Utilizing the 15 kV SiC IGBT, higher frequency chopping is possible which is speculated to decrease the size, weight, and losses thereby making it a conceivable idea to replace traditional transformers. The material cost would also be lesser as the use of copper in such SSTs, would be much lesser as compared to traditional transformers.

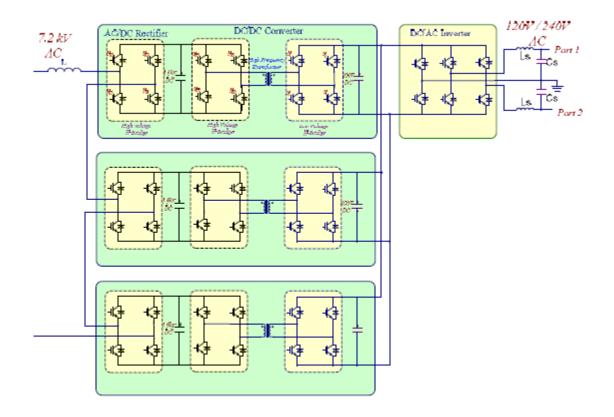

2.1.2 SST converter stages and its simulation parameters The SST consists of 3 stages i.e.

- 1. AC-DC rectifier

- 2. DC-DC Dual active H bridge (DAB)

- 3. DC-AC inverter

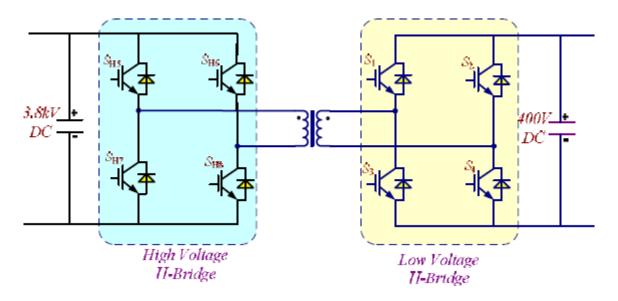

Figure 2.1. SST topology [13]

The model is replaced by an average simulation model by substituting the switching variable with continuous values which are averaged for 1 period of a switching cycle. In its basic system setup, the SST is a 20 kVA transformer connected to a 12 kV distribution system with a single phase output of 120 V. Single phase input voltage: 7.2 kV AC, 3 DC-DC link that convert 3800 V DC (HV side) to 400 V DC (LV side) and voltage source inverters that converts 400 V DC to 120/240 V AC at 60 Hz for 1 phase 3 wires. The switching devices that are used for the H bridges in the DAB and inverter are 6.5 kV silicon IGBT for the high voltage H bridge ( $f_s = 1 \text{ kHz}$ ) and 600 V IGBT for the low voltage H bridge ( $f_s = 10 \text{ kHz}$ ). 20 kVA model can be considered as a building block and can be used to make large 200 kVA models.

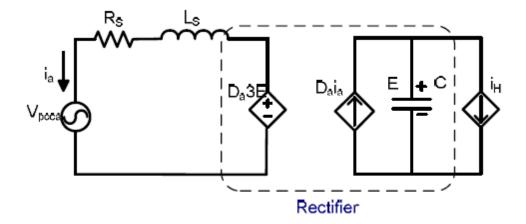

## 2.1.3 Rectifier modelling

The AC/DC rectifier converts the single phase 7.8kV AC voltage to 3 DC output of 3.8 kV while maintaining unity power factor at the input side. Utilizing the two current and voltage equation

$$L.\frac{di}{dt} = v_L(t) \tag{2.1}$$

$$C\frac{dv_c}{dt} = i_C(t) \tag{2.2}$$

Voltage equation for the circuit

$$L_s \frac{di_a}{dt} + V_{pcca} + R_s \cdot i_a = 3Ed_a \quad (2.3)$$

$$\frac{di_a}{dt} = \frac{3E}{L_s}d_a - \frac{V_{pcca}}{L_s} - \frac{R_s i_a}{L_s}$$

(2.4)

Where

$i_a = AC$  side input current,  $V_{pcca} = AC$  side input voltage,  $L_s =$

AC side input inductor,

$E = voltage \ of \ the \ dc \ bus, d_a = rectifier \ duty \ cycle \ for \ the \ PWM$

For the next current equation

$$C\frac{dE}{dt} + \frac{E}{R_I} + d_a i_a = 0 ag{2.5}$$

$$\frac{dE}{dt} = \frac{-E}{R_L C} - \frac{d_a i_a}{C} \tag{2.6}$$

Where C = rectifier DC capacitance

Based on these equations the equivalent average model is given

Figure 2.2. Equivalent average model [13]

In this case d-q control is used for the rectifier. An imaginary phase is developed which is 90 degrees lagging to the main phase A is hypothesized. Now the differential equation for the voltage and current for the imaginary phase will be

$$\frac{di_m}{dt} = \frac{3E}{L_s}d_m - \frac{V_{pccm}}{L_s} - \frac{R_s i_m}{L_s} \tag{2.7}$$

$$\frac{dE_m}{dt} = \frac{-E_m}{R_I C} - \frac{d_m i_m}{C} \tag{2.8}$$

Where  $i_m$  is input current for the imaginary phase, combining equation sets 1.4, 1.6, 1.7 and 1.8 we get

$$\frac{\overrightarrow{d\iota_{am}}}{dt} = \frac{3E}{L_s} \overrightarrow{d_{am}} - \frac{\overrightarrow{V_{pccam}}}{L_s} - \frac{R_s \overrightarrow{\iota_{am}}}{L_s}$$

(2.9)

$$\frac{dE_m}{dt} = \frac{-E_m}{R_L C} - \frac{\overrightarrow{d_{am}} \overrightarrow{\iota_{am}}}{C} \tag{2.10}$$

Where

$$\overrightarrow{\iota_{am}} = \begin{bmatrix} i_a \\ i_m \end{bmatrix}$$

, and  $\overrightarrow{d_{am}} = \begin{bmatrix} d_a \\ d_m \end{bmatrix}$ ,  $\overrightarrow{V_{pccam}} = \begin{bmatrix} V_{pcca} \\ V_{pccm} \end{bmatrix}$  (2.11)

The single phase dq transformation is applied to the equations 1.9 and 1.10, and the differential equation is obtained

$$[x]_{dq} = [T].[x]_{am}$$

(2.12)

Where

$$T = \begin{bmatrix} \sin(\theta) & -\cos\theta \\ \cos\theta & \sin(\theta) \end{bmatrix}$$

,  $\theta = 2\pi f_L$ ,  $f_L$  is line frequency (2.13)

$$\frac{d}{dt} \begin{bmatrix} i_d \\ i_q \end{bmatrix} = \frac{3E}{L_s} \begin{bmatrix} d_d \\ d_q \end{bmatrix} - \frac{1}{L_s} \begin{bmatrix} v_{pccd} \\ v_{pccq} \end{bmatrix} - \begin{bmatrix} \frac{R_s}{L_s} & -\omega \\ \omega & \frac{R_s}{L_s} \end{bmatrix} \begin{bmatrix} i_d \\ i_q \end{bmatrix}$$

(2.14)

$$\frac{dE}{dt} = -\frac{E}{R_L C} - \frac{1}{2C} \begin{bmatrix} d_d \\ d_q \end{bmatrix}^T \begin{bmatrix} i_d \\ i_q \end{bmatrix}$$

(2.15)

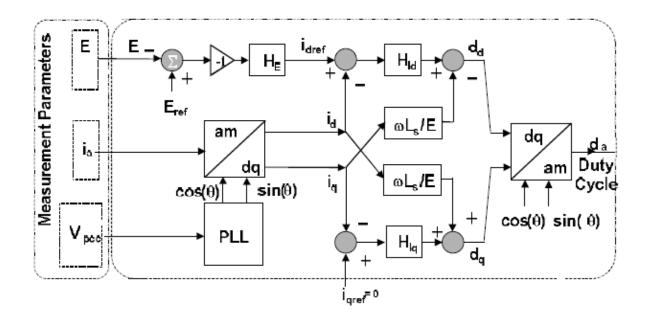

Using the phase locking loop in figure 2.3 below, the voltage vector is adjusted according to the direction of d axis during the steady state. Hence the grid voltage component in the q axis will be zero, while for d axis it will be equal to the grid voltage. Hence the d axis is the control for the active current, and q axis is for the reactive current component.

Figure 2.3. Dq controller for rectifier [13]

# 2.1.4 Modelling of the dual active bridge

Figure 2.4. Dual active bridge [13]

The DAB has 2 parts i.e. the HV Bridge and the LV Bridge. The rectifier regulates the high voltage side DC link voltage and the AC current is controlled to be sinusoidal. The low voltage DC link is controlled by the DAB converter. The dual active bridge scheme

provides zero voltage switching for all the switches, lesser voltage disturbances for the switches. The amount of power transferred being controlled by the phase angle difference and the magnitudes of the dc voltages at the two sending and receiving ends are given by the following equation.

$$P_o = \frac{V_{dc}V_{dc\_link}}{2Lf_H}d_{dc}\left(1 - d_{dc}\right)$$

(2.16)

V =input side high voltage DC voltage, H f is switching frequency, L is leakage inductance, dc \_link V is the secondary side low voltage DC link voltage referred to the primary side and  $d_{dc}$  is ratio of time delay between the two bridges to one half of switching period.

### 2.1.5 Modelling of the inverter stage

The DC/AC inverter changes the 400V DC to 240/120V AC, 1 phase/3 wires. The topology is shown in Fig.2.5 below. The inverter consists of six switches with three phase legs. The neutral point is joint to the third leg of the phase. The other two phase legs consists of four-switch inverters that are regulated by Sinusoidal Pulse Width Modulation (SPWM). The third leg connected to the phase in the six-switch inverter normally is regulated to give a square waveform to deliver as the neutral phase and at same time achieve the maximum employment of the DC bus voltage.

Figure 2.5. DC/AC inverter topology [13]

### 2.2 Relay protection design [6]

The protective relay system design usually has circuit breakers, current transformers and relays which must coordinate together to function properly. Protective relays or systems are usually not required to operate during normal operation, but must be able to act swiftly during fault incidence so as to avoid serious outages and damages. Usually a relay system's operating life will not be more than a few seconds, even when they might be connected to the system for many years. So testing becomes a very important part for these relays where they are put through immense conditions for long periods of time.

In normal day to day use there are four factors that *influence protection applications* are

- 1. Economics-Operation and maintenance cost

- 2. Magnitude and level of Fault-Fault levels and positioning of voltage and current transformers

- 3. Operating Practices-Accepted and practiced standards for efficient and strong performance

- 4. History of the type of fault that usually occur-Past History on the type of fault occurring and the forecast of likely such events

#### 2.3 Design criteria for protection applications [6]

In most cases the power system is divided into several zones of protection, each requiring its own set of relays, CT's and PT's. The following points are considered for *designing a protection system*

- a. Reliability-The Reliability of the system includes two elements dependability and security. Dependability is the correct operation in response to a problem in a system. Security is the amount of certainty that the relay will not operate in an inappropriate manner. Unfortunately both these aspects oppose one another, increasing security decreases dependability and vise a versa.

- b. Speed- As it takes only a couple of seconds to destabilize a system, so speedy operation of protection system becomes very important. But by increasing the speed, there can also be increase in unwanted or unexplained operations. High speed mostly indicates that the trip times are not higher than 50 ms (around 3 cycles of a 60 Hz system).

- c. Performance and Economics-Relays usually have set zones of protection provide better selectivity but they cost more in such cases [6].

#### 2.4 Zones of Protection [6]

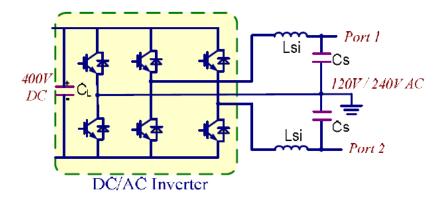

In power systems, a more general system configuration is to divide a system into protective zones. Now if a fault occurs inside the protective zone, appropriate action will be taken to isolate the particular zone from the rest of the system [6].

- Zones are usually defined for:

- a) Generators,

- b) Transformers,

- c) Buses,

- d) Transmission and distribution lines, and

- e) Motors.

Shown in Fig 6 is the concept of zone protection. Each zone is characterized by a closed, dashed line. Zone 1, for instance, has a generator and a transformer leads. Usually a zone might have more than one component. For example, zone 3 contains a generator-transformer unit and a bus connection leads, and zone 10 has a transformer and a line.

Fig 2.6. Protection Zones in a power system [6]

#### Following are a few characteristics of Zones of protection [6]

- Zones are always overlapped.

- Circuit breakers are located in the overlap region.

- For a fault in a particular zone, all the CB in that zone open up to isolate the fault.

- Usually one CB to another CB can be used to define a protective zone.

- Neighboring zones are overlapped to escape the option of unprotected areas. With

no overlap the area between two adjacent zones would not be in any zone and hence

would not be protected.

- As isolation during faults is done by circuit breakers, they should be placed in between devices in a zone and connections to the system i.e. breakers should be placed in each of the overlap region [6].

#### 2.5 Different types of protection schemes used

#### 2.5.1 Overcurrent protection [12]:

Mostly, there are two kinds of overcurrent relays used in the industry:

- 1. Instantaneous overcurrent relay: These relays operate as the name suggest instantaneously/immediately. The sensing relay trips when the current reaches the threshold limit. They are popularly utilized in bus/feeder protection. The instantaneous overcurrent relay is very helpful for protecting electrical units against high short circuit fault currents [14] [15].

- 2. Time-delayed overcurrent relays: a time-order system is applicable to implement the back-up protection system. Time-current curve are applied in such a manner that the operation time is inversely proportional to the fault current. If the fault current is lager, the relay will operate even faster. The general equation for the time overcurrent relay is:

$$\tau = \frac{K}{\lceil (PSM)^n - 1 \rceil} \tag{2.17}$$

$\tau$  = operation time PMS= plug multiplier setting K, n= preset constants.

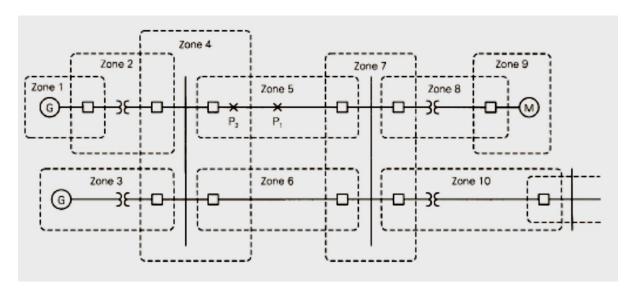

There two most important settings for the time-delay overcurrent relay are the pickup value, and the other is the time delay. Time-delay overcurrent relays operate at a faster rate at high current as compared to slow operation at lower levels of fault current. Thus the curve follows an inverse time characteristic shown in the figure 2.7 below. Time overcurrent relays have five different types of curves that are based on the slope of the time-overcurrent characteristic.

- Definite time

- Moderately inverse

- Inverse

- Very inverse

- Extremely inverse

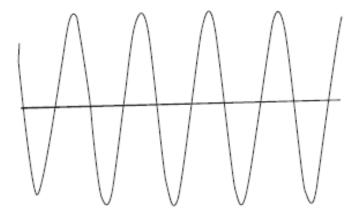

Fig 2.7. is the graph for a general inverse-time—overcurrent relay characteristics. The curves are set for a fault current with time delay of 0.2 sec and fault current around 20 times minimum pickup current [6].

# 2.5.2 Differential Relays

Differential protection scheme is a widely used protection scheme especially for unit protection like key component protection in power system like bus, generator, and transformers.

### 2.5.3 Principle of current differential relay

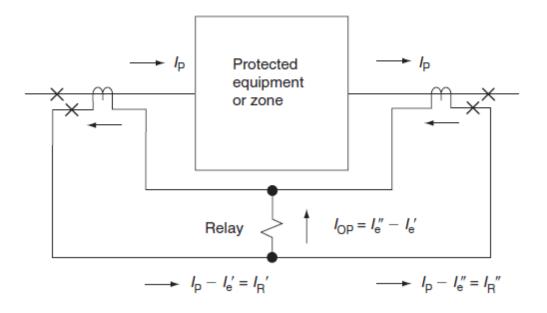

The operating principle for a traditional differential protection scheme is that the pickup current should be equal to the difference of the currents coming through the operating coil, and its working principle is based on Kirchhoff's current law.

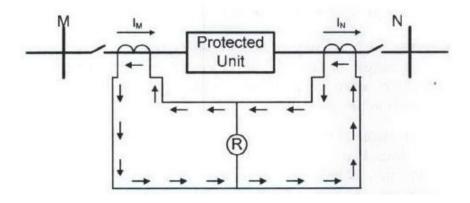

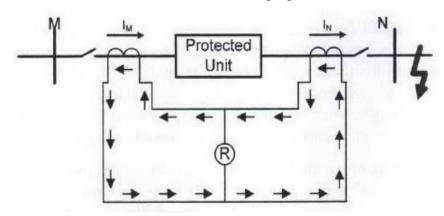

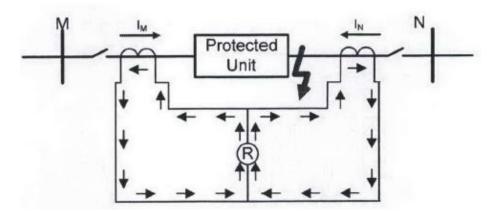

Figure 2.8. Currents in the differential system during normal operating condition when there is no fault [17]

Figure 2.9. Currents in the differential system during in case of external fault [17]

Figure 2.10. Currents in the differential system during in case of internal fault [17]

For the normal condition (shown in figure 2.8.), the currents at each side of the CTs are exactly equal in magnitude and opposite in phase. Thus, the secondary current that circulates in the pilot wire circuit doesn't produce a trip. On a fault taking place outside the zone of protection (shown in figure 2.9.), the differential relay still has no current flowing into the relay as the currents in both the CTs rises in magnitude at the same time. Hence no trip is produced. When a fault actually happens inside the zone of protection, the current

$I_M$  (shown in figure 2.10.) will no longer be equal to  $I_N$ , as hence, the imbalance current flow through the operating coil, after which the trip is generated.

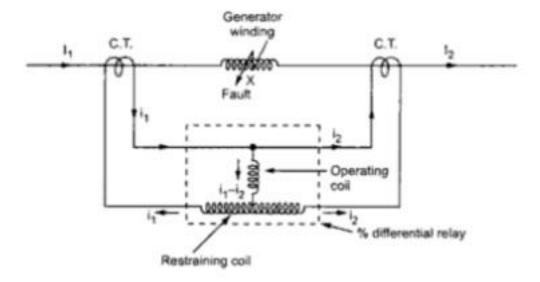

#### 2.5.4 Percentage Differential Relay

The traditional percentage differential has two coils as shown in figure 2.11 below: One is the biased coil that acts as the restraining coil, while the other is the operating coil. The bias or percentage differential is defined as the following quantity

$$Bias = \frac{(i1 - i2)}{(i1 + i2)/2} \tag{2.18}$$

The operating condition is defined as

$$Iop = \frac{(i1 - i2)}{(i1 + i2)/2} > bias current$$

(2.19)

Figure 2.11. Percentage differential relay schematic (18)

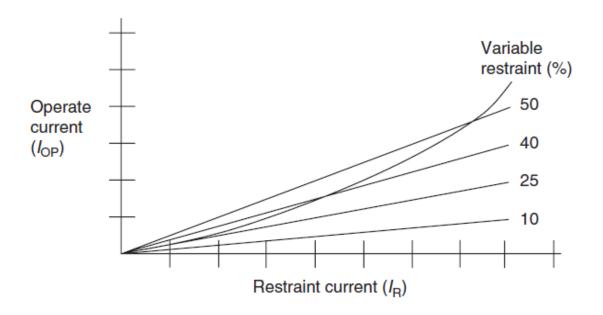

Differential relays either have fixed or variable restraint that help to operate the relay.

These restraining coils may have fixed or variable percentages, and general percentage

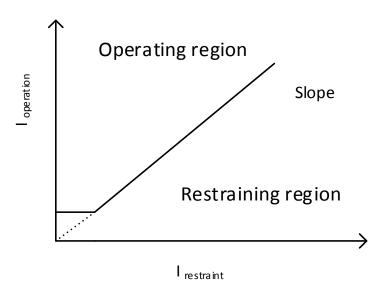

differential slope characteristic s are shown in Figure 2.12. The X axis is the restraining current  $I_R$ . The Y axis is the operating current  $I_{OP}$  required to operate the relay. Fixed percentage of the relays are usually between 10 % and 50% and they might have tap changers to modify the percentage.

Figure 2.12. Common percentage differential protection characteristic [6].

#### 2.5.5 Pilot Protection

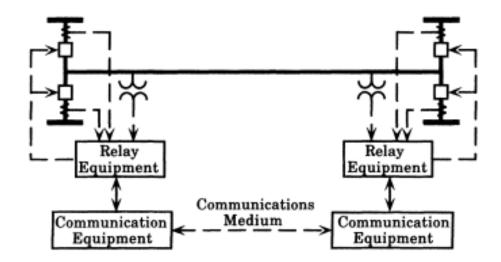

Pilot protection utilized for line protection gives high-speed instantaneous detection of phase-type and ground-type faults for 100% of the protected section from all terminals. This is the optimal primary protection intention. These systems utilize a communication path to send signals from the relaying system from one end of the line to the other end. The functioning principle is to compare the two relays for their currents at each terminal of the transmission line. If the two currents are equal, there is no fault on the transmission line, else when the two currents are not equal, there is a fault in the transmission line.

Figure 2.13. Topology schematic of pilot protection [19]

The pilot protection systems can be divided into two categories:

- 1. with use of channel:

- a. Channels is not vital for trip operations; also known as blocking systems

- b. Channels is required for trip operations; also known as transfer trip systems

- 2. With use of fault detection principle i.e. the comparison at the following quantities at several terminals:

- a. Power flow is measure between the terminals, also known as directional comparison

- b. The relative phase position of the currents are measured between the terminals, also known as phase comparison

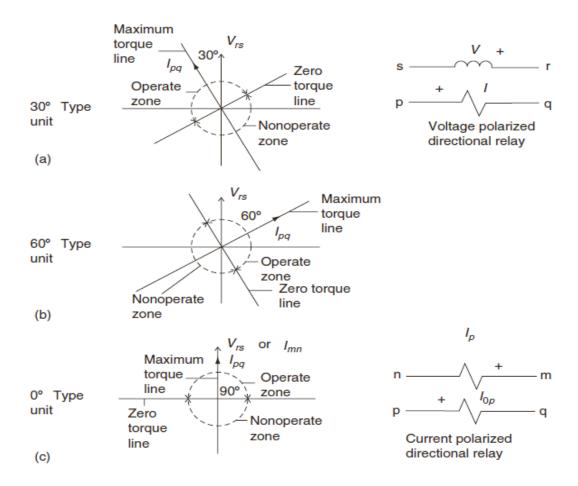

#### 2.5.6 Directional overcurrent protection

The directional overcurrent relays depends upon a reference voltage phasor, for estimating the direction of the fault. For all functional purposes, the system voltages do not change their phase positions much when a fault takes place. In comparison, line currents can deviate about 180 degrees (approximately reverse to the direction or flow) for faults that

take place on one side of the CT relative to a fault on the other side of the CT. After a fault occurs, the fault current has a characteristic phase angle approximately analogous to the voltage phasor. Hence the fault direction is decided by analyzing the current phasor with respect to the reference voltage phasor measured at the measurement location on the power line. This requires measurement of both current and voltage, hence it is costlier.

Figure 2.14. Directional relay operating characteristics [6].

#### 2.6 Use of pilot line differential protection: a comparative study

This is a compilation of literary papers to justify the use of differential protection with communication link being fast, selective, reliable and robust in smart grid systems like the FREEDM system.

#### Definitions

Micro grid: The term micro grid is used for a low-voltage (LV) network smart grid with island-operation capability.

Smart grid: A smart grid is a modern electrical grid that utilizes digital information and communications technology to collect and operate on that data, in a programmed manner to better the efficiency, reliability, robustness, and cost effectiveness of the generation, transmission and distribution of electricity

# 1. Differential protection of micro grids with central protection unit support [20]:

Traditional fault current detection usually fail in micro grid systems because of a number of reasons like loop systems, higher fault current levels in looped system, and other factors [7] [8]. It is an extremely important aspect to estimate the fault currents due to inverter based DGs. Using differential protection system is advantageous as the system doesn't require prior knowledge of fault currents and value. Hence due to the ever changing fault current levels, differential protection is favored as it can easily adapt to such changes. It doesn't require prior knowledge or previous working's data. The differential protection system is also immune to operate without voltage fluctuations. The differential system can also easily adapt to the new configurations, new developments and infrastructure. Thus differential protection is considered to be one of the main contenders for development of

protection systems for micro grids. However long transmission/distribution lines require communication setup for employing differential protection. The differential protection can be applied to an entire system by using an advanced communication link for data processing.

#### 2. Universal pilot wire differential protection for distribution systems [21]

This paper shows a unique pilot wire differential protection scheme for distribution systems. The ideas and principle of the traditional pilot wire differential protection is adopted here. After which many varieties of numerical differential protection schemes utilizing the pilot wires as communication channels have been shown in the paper. Current differential protection has always been accepted in power systems because of high robustness, precision, and sensitivity. Current differential based on application can be classified as the following types of protection system.

- 1. Pilot wire protection

- 2. Micro wave communication protection

- 3. Optical fiber communication protection

- 4. Power line carrier protection

# Communicating line differential protection for urban distribution networks [22]

Increasing reliability of system is of paramount importance, as most systems are changing from radial systems are changing from radial systems to closed loop/ meshed systems.

Using communication links, the paper authors have developed a type of protection using

differential current protection principle. The differential protection scheme is adopted because for loop systems with continuously varying line conditions the following protection methods can be used.

- 1. Directional over current protection

- 2. Distance relay

- 3. Line differential protection

Selectivity is an extremely important factor i.e. a particular part of the network remains unaffected by faults outside its zone of protection. Considering this fact, for the above mentioned statements will have the following differences.

- Distance protection will require a PT/VT for voltage measurement, and is not recommended for short lines without communication and back up protection. But they can act as good back up protection with over reaching capability. Also a (V/F) protection is also required with this unit.

- Directional over current protection also requires a VT/PT for voltage measurements. Mostly it requires communication channel for internal communication between several related function making the communication channel heavily loaded. Also the specifications are difficult to calculate and also the trip times are not extremely fast.

- As compared to the mentioned lines above, the pilot differential protection system has extremely fast trip timings. The relays require communication link between them. It cannot be used for large distances without communication link. The functionality is well tested and observed. Over current protection is also required

as an added protection. Earth fault protection application also can be included into the protection system.

Considering all the factors, the authors concluded that for the modern power system with loop/meshed networks line differential protection is a good fit.

#### 4. Protection principles for future micro grids [23]

Traditional fuse protection systems cannot be used in LV micro grid distribution systems because of limited fault current feeding capabilities of converters/limiters limiting the fault current [23]. Hence the protection system for a micro grid must include the following properties.

- Adaptive capabilities

- High speed communication

- High speed trip detection and operation inside the micro grid

- Unnecessary tripping of micro grid for fault on network and vise a versa

Based on the following literary reviews it shows that utilizing a fast differential pilot protection scheme could be an answer to the some of the problems faced by protection systems in smart grids/micro grids.

#### **CHAPTER 3**

# UPDATED ALGORITHM AND THE COMPARISON OF THE HARDWARE TEST AND SIMULATION RESULTS

#### 3.1 Intelligent fault management system theory [12] [24]

The IFM (Intelligent Fault Management system) is an algorithm for the application of distributed grid sense for the FREEDM system architecture. The algorithm is a complete protection system that is running in the background constantly by the central processing unit. The Intelligent Fault Management system detects and isolates fault on the 12.47 kV side i.e. the main loop of the FREEDM system. The Intelligent Energy Management (IEM) communicates with the IFM through RSC channels. The IEMs record the power flow injections in the load distribution system. Both the solar and wind injection are integrated through the IEMs. Hence the IEMs can provide consultative process request on real time energy basis future market forecasts as well. So when a fault occurs, the IFM detects the fault location and the trip signal is sent to the corresponding Fault Isolation Devices (FIDs) which isolate the fault.

Distributed Grid Intelligence (DGI) controls the entire operation of the FREEDM system.

The DGI is assigned to the IEM and IFM devices. So both the IEM and IFM devices will run the DGI software.

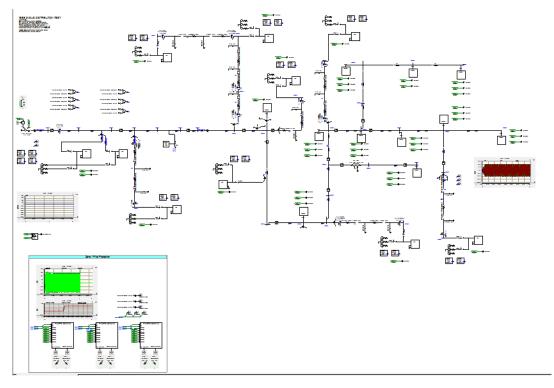

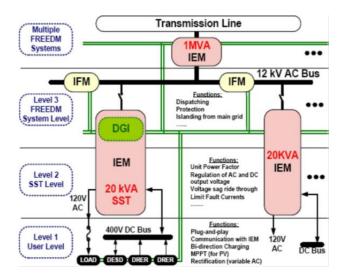

Figure 3.1. FREEDM model with multiple levels of control put reference [24]

Above shown is the FREEDM control system architecture of the FREEDM control system architecture. The levels are explained as following [24].

- Level 1- This is the user level , where in residential loads, batteries and other DESDs connected to the grid are shown

- 2. Level 2-This level is at the SST (Solid State Transformer) level. In this the IEM regulate, manage and control the power flow of different DRERs (solar, wind).

- 3. Level 3- This is the level for the FREEDM system control and is present in all the IEM and IFM devices through the DGI software.

#### **3.2 Protection Zone Concept**

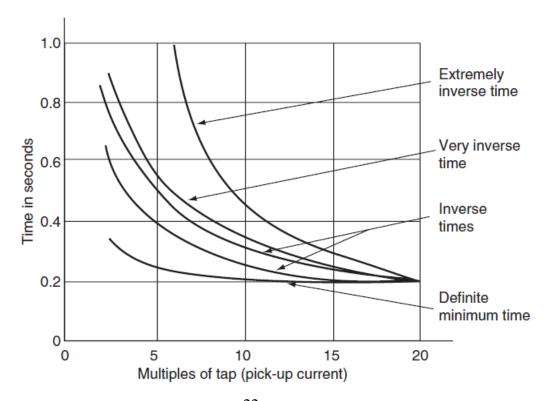

Protective zone concept is applied to the FREEDM system in which the system is divided into multiple zones, using the FIDs. The FIDs act same as a normal Circuit Breaker, the only difference being that the FIDs are capable of extremely fast current interruption in matter of micro seconds [Put reference]. The loads, DRERs and the DESDs are maintained

through the SST. So if a fault were to occur inside the zone, the FIDs at the end of the zone will operate to isolate the fault from the main loop. And also the SST connected to that zone will shut down, so that the local distributed generation is not affected by this fault. The FREEDM protection strategy is shown in the figure below.

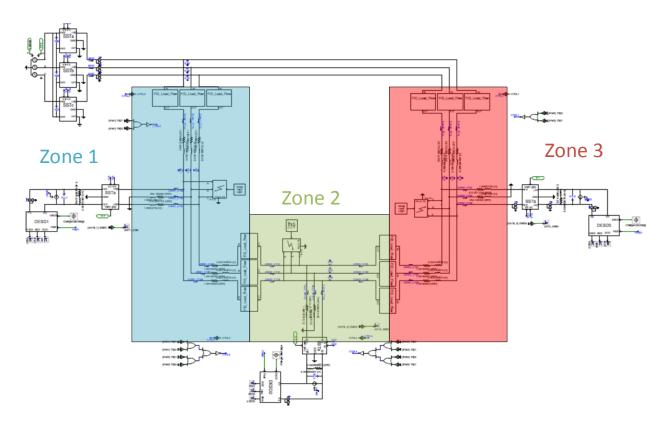

12.37 kV Bus Current limiter Current limiter Zone 0 Relay Relay Relay Zone 3 Zone 1 Relay Relay Relay Relay Relay Relay Zone 2 Relay

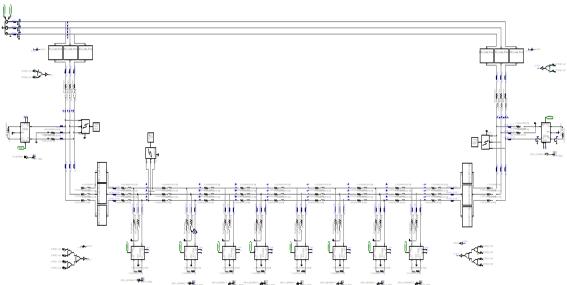

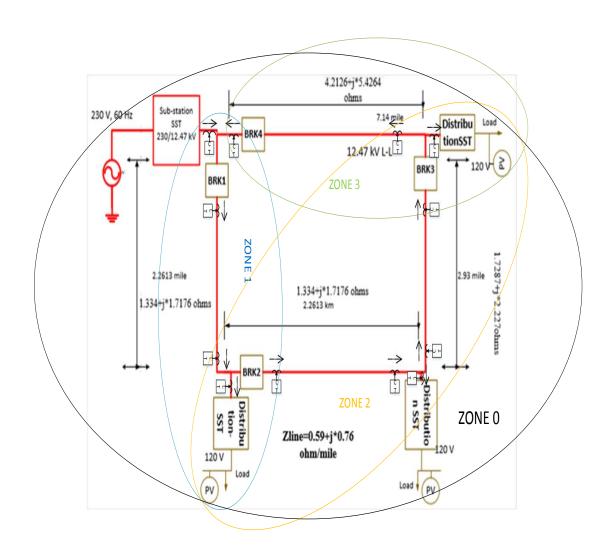

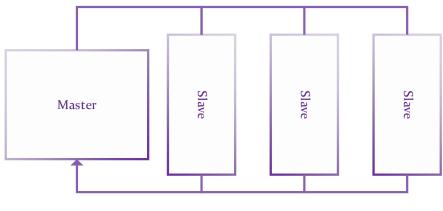

Figure 3.2. IFM zones of protection strategy [4]

Figure 3.3. Alternate concept of the IFM zones of protection in FREEDM [5].

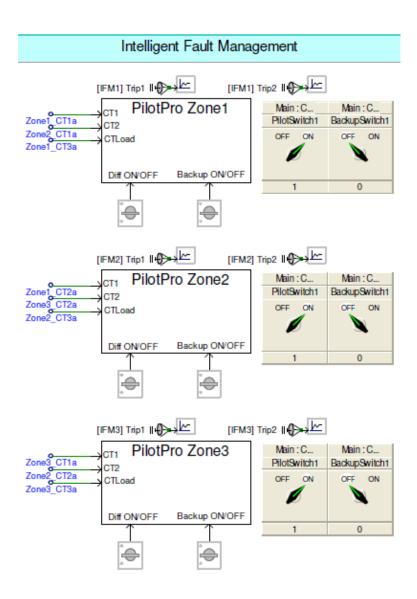

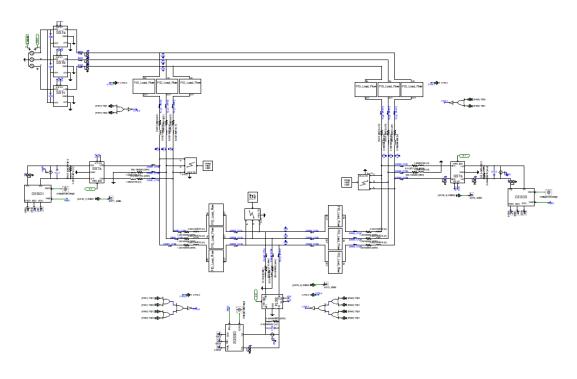

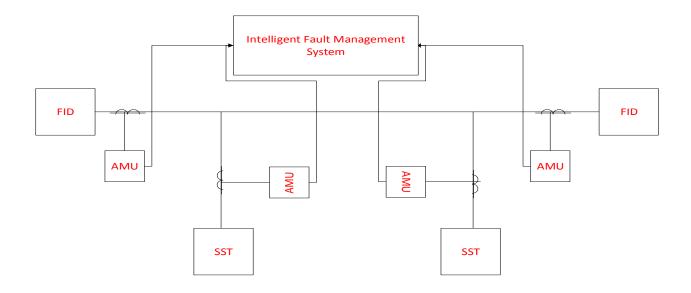

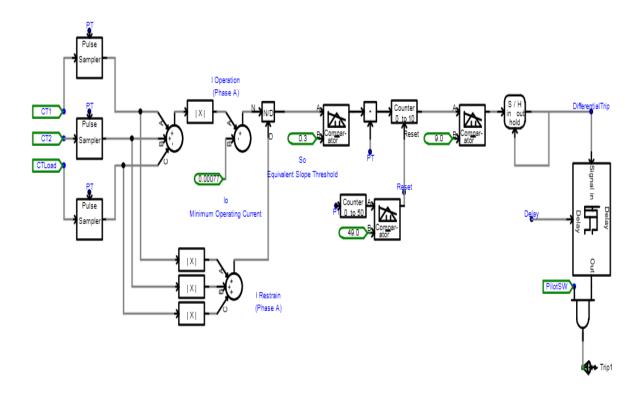

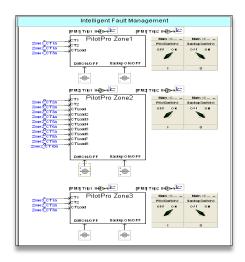

Above shown is the FREEDM zones of protection strategy in which there are 3 zones of protection and 1 large protection zone which includes the other 3 zones called Zone 0. The Zone 0 protection scheme will be seen as a backup protection scheme for the FREEDM system. The Novel fast pilot differential protection developed previously developed will be employed in each of the three zones. The Analog Merging Units (AMU) are connected to each of the terminals of the FIDs, SST primaries to record and digitize the magnitude of the current, and transmit the data back to the IFM. Every Zone has a separate IFM which will be running the DGI software with the pilot protection algorithm embedded in it [put reference].

The primary protection scheme is based on differential protection employed in each zone [5] [12]. The sum of currents in any particular zone should be zero. This demonstrates that either there is no fault inside the zone or fault exists outside the zone (also for which the protection unit doesn't trip). Now if the sum of currents in the zone is not zero, in that case, the faults exists within the zone, and then the IFM transmits the signals to the terminal end FIDS and SST in that particular zone to open up the zone and clear the fault on the main loop. All the samples sent from the AMU to the IFM have GPS time stamps to ensure the accuracy of the protection system algorithm. Here the SST acts as C.B/switch between the main loop and the secondary distribution system, and so the firing angle of the SST is made

zero during a fault, so as to disconnect the SST. The switching delay time for the SST is very less.

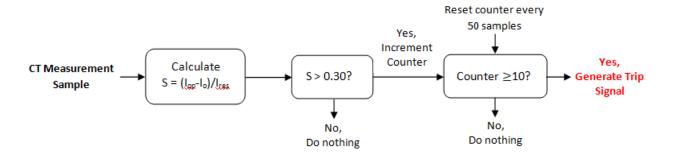

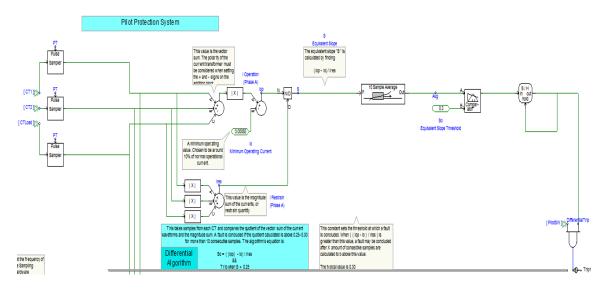

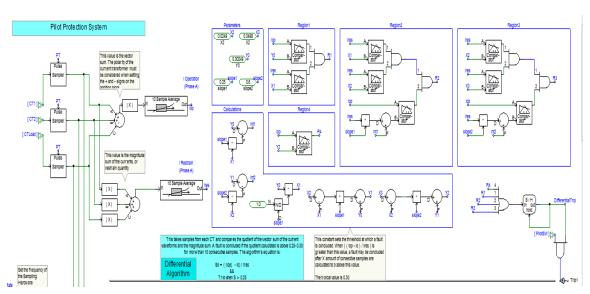

The IFM collects all the samples values from the AMU with identical time stamps and sums up all the currents in the zone and is the sum is zero in that case there's no fault, now if the sum is not zero, it holds the samples and analyses the next incoming data. For the next 10 samples, if the sum is still not zero, in that case the IFM declares a fault and sends a trip signal. If for the next 10 samples, the sum of the currents is zero in that case, there is a fault declared and the IFM resets the counter. The protection algorithm is employed through microprocessors [12].

The secondary protection algorithm is an overcurrent protection algorithm. In this scenario the IFM analyses all the current samples, and then compares it to a preset value that is 3-5 times the rated current. If the sample is greater than the prefixed value for the next 15-20 samples, in that case the IFM issues a trip signal to the FIDS. And if it doesn't last for 15-20 samples, then no trip signal is issued by the IFM. Zone 0 will act as backup protection of Zones 1, 2, and 3. Usually the measured values of the current in zone1, 2, and 3 are compared and the difference of the magnitude and direction of the currents are sent to the IFM. The coordination between Zone 0 and Zones 1, 2, and 3 are done in such a way that the protection algorithm is exactly the same, but the evaluation time is 5-10 times that of other zones/ so it will only operate when the zones 1, 2, and 3 protection algorithms fail to operate. So I this case the IFM provides both primary and backup protection.

Figure 3.4. IFM system with the in cooperation of the AMUs

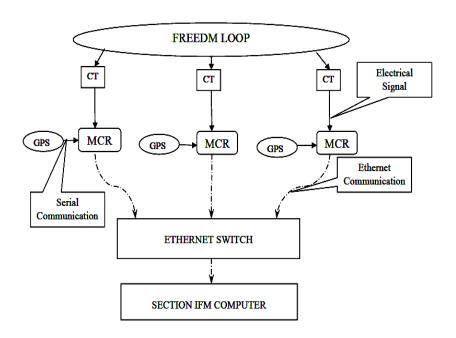

#### 3.3 Sampling data

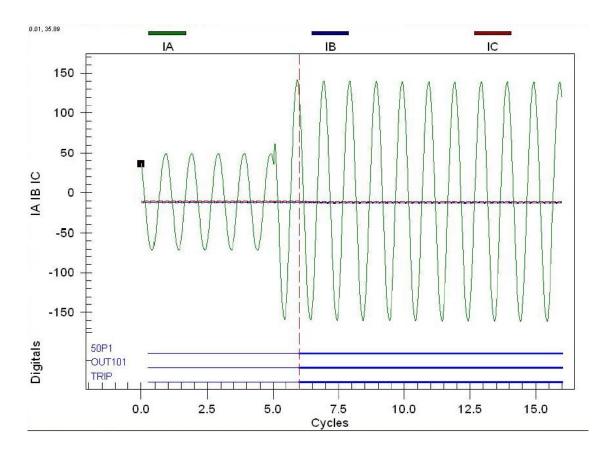

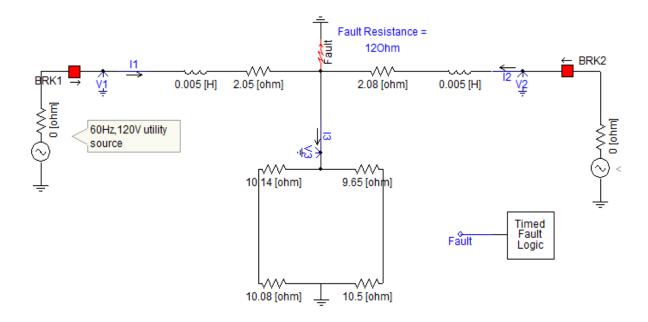

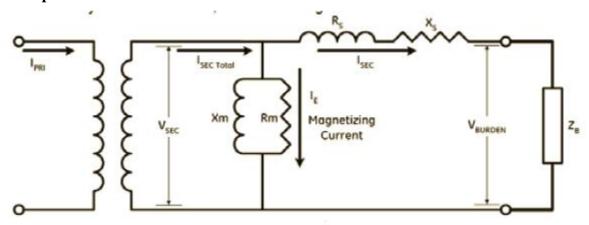

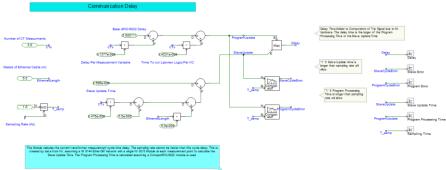

The speed, accuracy and precision of the IFM protection algorithm depends on the execution, sampling and communication method. The current from the CT is converted into a voltage signal by keeping a small resistor on the secondary side of the CT. The AMU consists of a microcontroller, which samples the analog voltage signal and gives data in a digital form. GPS (time stamps) are also added by the AMU, so that only data with similar time stamps are used in the algorithm by the IFM. So the IFM collects the sampled data with similar time stamps. It makes a sum of these sampled values from continues measurements, to see if the sum is zero or not. A tolerance of 5 % is assumed which defines the minimum operation current for the protection algorithm. For a fault, the IFM will hold down and count the next incoming samples. It will make a sum of the next 10 samples with time stamps, which would be 2 ms for a 100 samples/cycle measurement. If the sum of the